传统的数字锁相环设计在结构上希望通过采用具有低通特性的环路滤波,从而获得稳定的振荡控制数据。但是,在基于数字逻辑电路设计的数字锁相环系统中,利用逻辑算法实现低通滤波是比较困难的。于是,出现了一些脉冲序列低通滤波计数电路,其中最为常见的是“N先于M”环路滤波器。这些电路通过对鉴相模块产生的相位误差脉冲进行计数运算,获得可控振荡器模块的振荡控制参数。脉冲序列低通滤波计数方法是一个比较复杂的非线性处理过程,难以进行线性近似,所以无法采用系统传递函数分析方法确定锁相环中的设计参数,以及进一步分析锁相性能。在设计方法上多采用VHDL语言或者Verilog HDL语言编程完成系统设计,并利用EDA软件对系统进行时序仿真,以验证设计的正确性。该种设计方法就要求设计者对FPGA硬件有一定的了解,并且具有扎实的硬件描述语言编程基础。

本文采用一种基于比例积分(PI)控制算法的环路滤波器应用于带宽自适应的全数字锁相环,建立了该锁相环的数学模型,并分析该锁相环的各项性能指标和设计参数之间的关系。利用DSP Builder直接对得到的锁相环数学模型在Matlab/Simulink环境下进行系统级的建模,并进行计算机仿真,同时将建立的模型文件转换成VHDL程序代码,在QuartusⅡ软件中进行仿真验证,并用FPGA予以实现。

1 带宽自适应全数字锁相环的理论分析

1.1 基于PI控制的模拟锁相环的理论分析

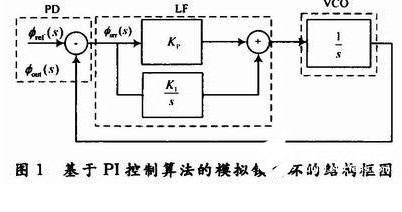

锁相回路是一个负反馈系统,主要由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三个部分组成。鉴相器的作用是计算输入信号和输出信号的之间的相位误差。环路滤波器的主要作用是抑制噪声及高频分量,并且控制着环路相位校正的速度与精度。为了能够提高锁相系统的性能,本文采用基于PI控制算法的一阶低通滤波器,即将鉴相模块鉴别出的相位误差大小乘以一定的比例系数而产生一个比例控制参数,同时对相位误差大小进行积分,并在积分系数的调节下产生一个积分控制参数,最终取比例和积分控制参数的和作为该环节的控制参数。压控振荡器的作用就是利用输入的电压值控制输出信号的频率。设压控振荡器的输入信号为V0(t),输出信号的频率为ω0+KV0(t),则输出信号的相位:

式中:,则压控振荡器的传递函数为:HVCO(s)=θf(s)/V0(t)=K/s,可以看出压控振荡器相当于一个固有积分环节。在该设计中取压控振荡器的增益K=1,则通过以上的分析可得基于PI控制算法的模拟锁相环结构框图如图1所示。

由图1可以得出,该锁相回路的闭环传递函数为:

不难看出该系统是一个典型的二阶系统,那么二阶模拟锁相环的闭环传递函数可表示为:

式中:Kp和Kl分别为比例系数和积分系数,取为系统的自然频率;ζ为系统的阻尼系数。

1.2 带宽自适应全数字锁相环的理论分析

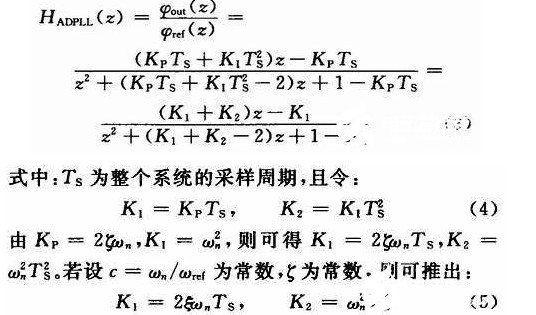

对上述模拟锁相环的s域传递函数进行离散化处理,采用脉冲响应不变法即可得到全数字锁相环回路的闭环传递函数为:

于是可以得到基于参数K1和K2的全数字锁相环的结构图如图2所示。

分析式(5)中得到的两个参数K1和K2,若式中c和ζ为常数,则参数K1和K2的变化只与输入信号频率ωref的变化有关,因此,得到的全数字锁相环模型具有自适应的特性,这是传统的全数字锁相环不具有的新特点。

2 带宽自适应全数字锁相环的DSP Builder建模

2.1 DSP Builder介绍

由于FPGA广泛应用,使得EDA软件QuartusⅡ在很多领域中显得尤为重要,目前全数字锁相环的设计多是通过EDA技术完成,使用FPGA予以实现。这就需要设计者对FPGA硬件电路及硬件描述语言VHDL或者Verilog HDL非常熟悉;同时,由于在QuartusⅡ环境下使用硬件描述语言进行编程设计系统模块时相当繁琐。而Matlab在搭建系统的数学模型方面功能强大,具有专门的建模仿真工具Simulink,可以进行图形化的建模仿真。但是Matlab本身不支持硬件电路,只能完成单纯的数学模型的建模、仿真。如果把两者的优势结合起来,使二者扬长避短,则可以使复杂的电子系统的设计变得相当容易且直观。

DSP Builder是Altera公司推出的一个面向DSP开发的系统工具。它是作为Matlab的一个Simulink工具箱出现的,可以在atlab/Simulink环境下进行图形化建模仿真。DSP Builder中的模块是以算法级的描述给出的,易于用户从系统或者算法级进行建模,甚至不需要十分了解FPGA本身和硬件描述语言。在DSPBuilder的模块库中还提供Matlab和QuartusⅡ的接口模块Signal Compiler,利用该模块可以方便地把在Ma-tlab/Simulink环境下建立的算法或者系统级模型转化为FPGA可编译的后缀为.vhd的VHDL语言程序。在QuartusⅡ中打开工程文件,可以对生成的程序进行编译、时序仿真,完成后可以结合FPGA开发板的引脚情况锁定引脚,经过编译、适配后即可下载到FPGA开发板上完成硬件测试和硬件实现。

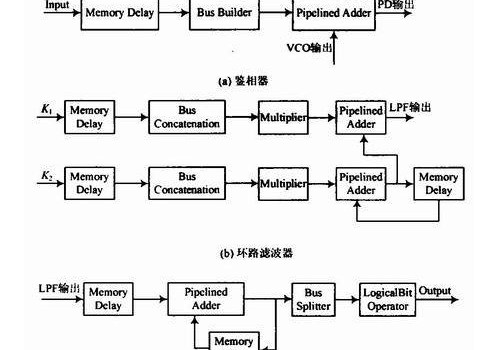

2.2 带宽自适应全数字锁相环的DSP Builder建模

该设计方法就是在Matlab/Simulink环境下借助DSP Builder简单、方便快速地建立上述分析得到的全数字锁相环的数学模型,各个模块建模方框图如图3所示。按照以上各个模块方框图连接,构成整个系统模型,并加入系统时钟Clock模块和Signal Compiler模块,即完成整个系统的。DSP Builder建模。其中输入信号K1和K2是由式(5)计算得到,用6位无符号整数表示,K1和K2可以随着输入信号Phi_ref频率的变化而自适应的做出调整;Phi_ref和Phi_out分别为环路的输入和输出信号,都采用1位无符号的整数表示。

3 带宽自适应全数字锁相环的软件仿真和FPGA实现

3.1 带宽自适应全数字锁相环的软件仿真

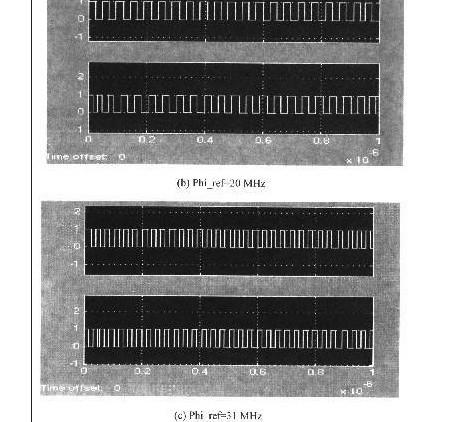

在图3建立的模型基础上,该设计首先对带宽自适应全数字锁相环进行了软件仿真,主要包括Matlab/Simulink仿真和QuartusⅡ时序仿真。其中系统的各个参数为:阻尼系数ζ=O.707,系统时钟周期Tclk=1/fs,采样频率fs=250 MHz。图4为输入信号Phi_ref取不同频率时的Matlab/Simulink仿真波形。

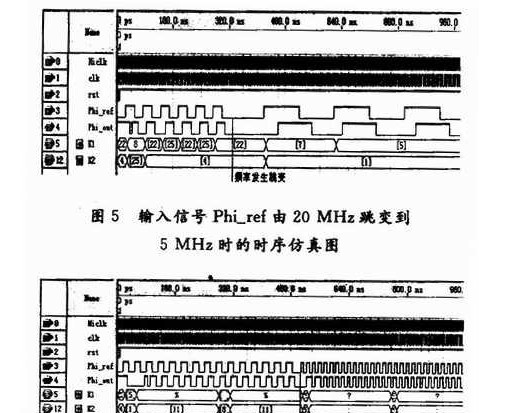

使用DSP Builder库中的Signal Compiler模块将图3建立的全数字锁相环模型转化为VHDL语言代码。该设计通过QuartusⅡ软件完成带宽自适应全数字锁相环的整体时序仿真。图5为输入信号Phi_ref由20 MHz跳变到5 MHz时的时序仿真图;图6为输入信号Phi_ref由31 MHz跳变到62 MHz时的时序仿真图。通过对所设计的全数字锁相环的Matlab/Simu-link仿真和QuartusⅡ时序仿真可以看出:该系统能够实现锁频的功能;同时该系统具有自适应的特性,在输入信号很大变化范围内都具有良好的性能;最后该系统对频率发生阶跃跳变的输入信号亦具有很好的跟踪性能。

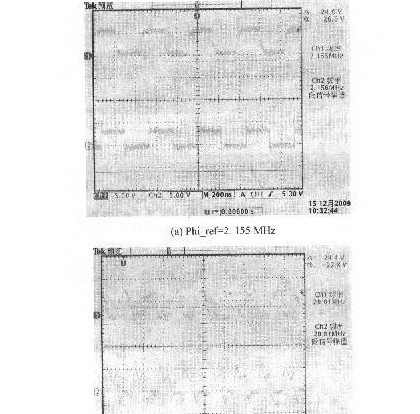

3.2 FPGA实现及硬件测试

由于Signal Compiler模块可以自动地将DSPbuilder建立的模型文件转化为QuartusⅡ环境下的工程文件,因此,该设计在完成软件仿真后结合FPGA试验箱,在生成的工程下进行引脚的锁定、编译适配下载到FPGA芯片,实现所设计的带宽自适应全数字锁相环,并完成硬件测试。在硬件测试中需要用到信号发生器和示波器,信号发生器用来产生锁相环的输入测试信号,示波器用来观测锁相环的输入/输出波形。图7为输入信号Phi_ref取不同频率时的实测波形。

以上的软件仿真与硬件测试都表明,设计的带宽自适应全数字锁相环系统能过实现锁频的功能,设计是成功可行的。

4 结语

本文使用DSP Builder建立系统模型完成全数字锁相环设计,理论分析和仿真结果基本一致。从以上设计过程可以看出:基于DSP Buil-der完成全数字锁相环设计的方法,使得设计者可以利用Simulink快捷灵活的建模仿真功能和Matlab强大的数据分析能力进行FPGA系统级的建模仿真,并使得设计者从编写VHDL或者Verilog HDL等代码语言的繁琐工作中解放出来,而专注于在Matlab/Simulink下搭建系统模型的工作上,缩短了设计周期,提高了设计的灵活性。

责任编辑:pj

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)