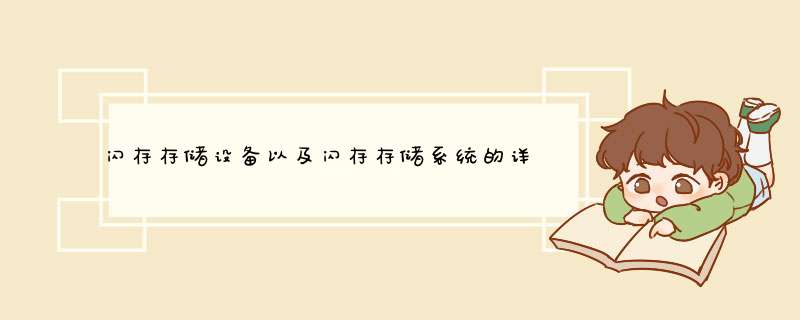

闪存设备

闪存设备的内部结构包含芯片、芯片控制器、存储处理器、缓存、控制器内存以及接口。目前主流的接口包括 UFS、SATA、PCIe 等

闪存内部结构

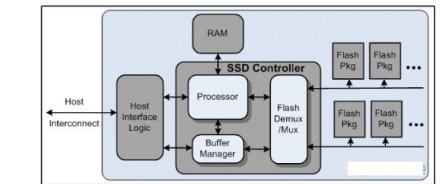

闪存存储系统

考虑的问题:

1. 传统的数据库设计是否适用高速的 SSD 呢?固态存储数据库设计

2. 传统的文件系统设计是否能够高效管理 SSD 呢?固态存储文件系统(F2FS)

3. 传统的调度器是否能够充分利用 SSD 呢?固态存储调度器(多队列)

4. 传统的系统架构是否适合 SSD 呢?固态存储系统存储架构

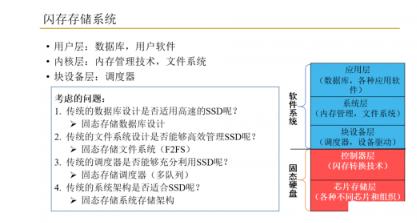

并行优化设计

接着,石亮教授介绍了团队研究的三份工作:1)基于闪存访问冲突最小化的并行优化设计

2)基于芯片空闲时间的垃圾回收导致访问冲突优化策略

3)基于闪存系统并行性最大化的性能优化设计

基于闪存访问冲突最小化的并行优化设计

问题:介绍闪存中存在的芯片利用率严重偏低问题,也就是闪存芯片同时被访问的数量不高,这主要是由 I/O 请求之间的访问冲突引起的。

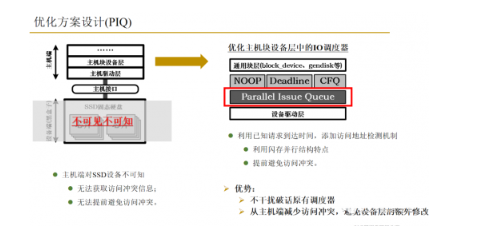

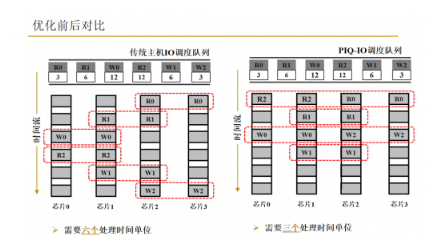

方案:石亮教授介绍了团队发表的一篇论文中的解决方案 Parallel Issue Queue(PIQ),旨在通过调度的方式最大程度地减少 I/O 请求之间的访问冲突。

PIQ 将没有冲突的 I/O 请求调度到同一批次中,将有冲突的 I / O 请求调度到不同的批次中。因此,通过利用 SSD 的并行性,可以同时满足一批中的多个 I/O 请求。

基于芯片空闲时间的垃圾回收导致访问冲突优化策略

ExploiTIng Chip Idleness for Minimized Garbage CollecTIon Induced Chip Access Conflict on Solid State Drives

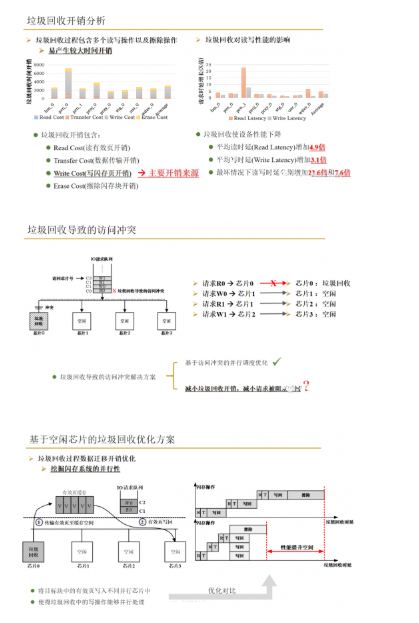

问题:由于闪存的非就地更新特征,内部将频繁执行垃圾回收 *** 作来回收无效页面,当频繁触发内部活动时,主机 I/O 性能将因它们之间的访问冲突而受到严重影响。

方案:为了改善垃圾回收产生的访问冲突引起的性能下降问题,石亮教授介绍了论文中的解决方法,提出了一种新的访问冲突最小化方案。介绍通过利用 SSD 的多个芯片的空闲时间来调度内部活动引发的 *** 作,以最大程度地减少访问冲突。

该方法通过两个步骤实现:首先,将内部活动访问的数据读取到控制器;其次,通过在内部活动期间利用空闲芯片,将内部活动访问的数据写回到这些空闲芯片。

基于闪存系统并行性最大化的性能优化设计

Parallel all the TIme:Plane level parallelism exploraTIon for high performance solid state drives

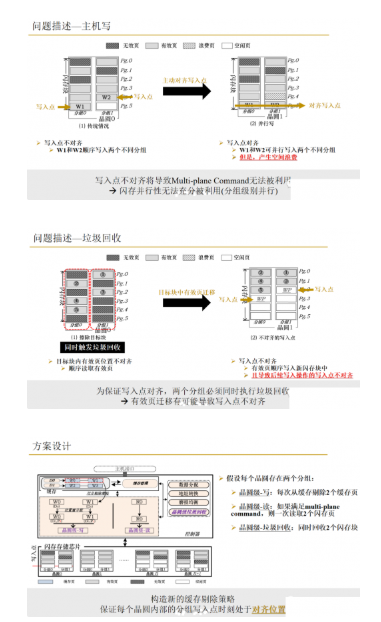

问题:闪存由多级并行性组成,包括 channel,chip,die 和 plane。在这些并行级别中,plane 级并行性具有最严格的限制。只能并行处理在不同 plane 中访问相同地址的相同类型的 *** 作。plane 级并行性还没有得到很好的利用,应该进一步改善。

方案:在这项工作中,石亮教授介绍了一个从 plane 到 die 的并行优化方法,以通过智能地满足严格的限制来利用 plane 级并行性。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)