可编程逻辑器件(Programmable Logic Device,PLD)起源于20世纪70年代,是在专用集成电路(ASIC)的基础上发展起来的一种新型逻辑器件,是当今数字系统设计的主要硬件平台,其主要特点就是完全由用户通过软件进行配置和编程,从而完成某种特定的功能,且可以反复擦写。在修改和升级PLD时,不需额外地改变PCB电路板,只是在计算机上修改和更新程序,使硬件设计工作成为软件开发工作,缩短了系统设计的周期,提高了实现的灵活性并降低了成本,因此获得了广大硬件工程师的青睐,形成了巨大的PLD产业规模。

1.可编程逻辑器件的基本结构

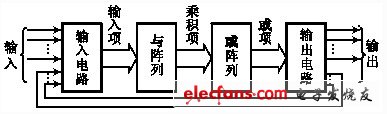

可编程逻辑器件(简称PLD)的基本结构是由它主要由输入缓冲、与阵列、或阵列和输出结构等四部分组成。如图1所示:

图1 可编程逻辑器件的基本结构

可编程逻辑器件的核心部分是可以实现与—或逻辑的与阵列和或阵列,由与门构成的与阵列用来产生乘积项,由或门构成的或阵列用来产生乘积项之和形式的函数。输出信号往往可以通过内部通路反馈到与阵列的输入端。为了适应各种输入情况,与阵列的每个输入端(包括内部反馈信号输入端)都有输入缓冲电路,从而降低对输入信号的要求,使之具有足够的驱动能力,并产生原变量和反变量(两个互补的信号。有些PLD的输入电路还包含锁存器(Latch),甚至是一些可以组态的输入宏单元,可对信号进行预处理。输出结构相对于不同的可编程逻辑器件(PLD)差异很大,有些是组合输出结构,有些是时序输出结构,还有些是可编程的输出结构,可以实现各种组合逻辑和时序逻辑功能。

2.可编程逻辑器件(PLD)电路表示法

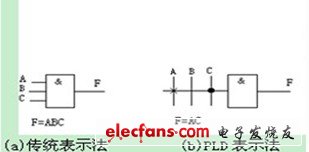

可编程逻辑器件电路表示法与传统表示法有所不同,主要因为PLD的阵列规模十分庞大,用传统的方法表示极不方便。图2中给出了PLD的三种连接方式。连线交叉处有实点的表示硬线连接,也就是固定连接,用户不可改变;有符号"X"的表示可编程连接,它通常表示此点目前是互连的,即编程熔丝未被烧断;若交叉点上没有"X"连线只是单纯交叉表示不连接或者是擦除单元。

图2 PLD的三种连接方式

如图3分别给出了传统表示法和PLD表示法的一个示例。显然,在输入量很多的情况下,PLD表示法显得简洁。由图可看出,三输入端与门的输入线只有一根线,一般称为乘积线,三个输入变量分别由三根与乘积线垂直的竖线送入,其中固定连接和编程连接的相应输入项为乘积项的一部分,不连接的输入线不作为乘积项的一部分。

图3 传统表示法和PLD表示法

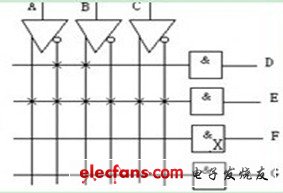

图4所示为三输入变量A、B、C分别通过具有互补输出端的输入缓冲器输入原变量和反变量构成的与阵列。第一个与门输出为D= B,第二个与门输出为E=A B C =0,这种状态称为与门的缺省状态,为了表示方便,可以在相应与门符号中加一个“×”,以代替所有输入项所对应的“×”。即如第三个与门所表示的那样,F=0。第四个与门与所有输入都不接通,即它的输入是悬空的,因此G=1,一般将其称作“悬浮1”状态。

图4 三输入变量A、B、C

可编程逻辑器件(PLD)的输出电路因器件的不同而有所不同,有些是组合电路输出,而有些则含有触发器单元,但总体可分为固定输出和可组态输出两类。由PLD的结构可知,最终在输出端得到的是输入变量的乘积项之和。众所周知,任何组合逻辑函数和时序逻辑电路的驱动函数均可化为与-或式(积之和)。因此,可编程逻辑器件(PLD)的这种结构与触发器(存储单元)相配合,对实现数字电路和数字系统的设计具有普遍的意义。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)