本文设计了一种采用增益增强结构的带开关电容共模反馈的折叠式共源共栅跨导运算放大器,可用于流水线结构的A/D中。出于对性能及版图因素的考虑,采用了单端放大器作为增益提高辅助放大器。并通过改进共模负反馈电路,使得放大器输出共模反馈电压稳定更快,抖动更小。本设计在Cadence环境下对运放的电路和版图进行了仿真。结果表明,放大器的各项性能参数达到了理想的效果。

1 电路结构的分析与设计

CMOS跨导运算放大器常用结构有两级放大结构、套筒结构和折叠共源共栅结构等形式。两级放大结构的运放电路结构虽然具有高增益、高摆幅等优点,但由于每一级至少引入一个极点,为了保障整个放大器的相频特性满足要求,需要额外的频率补偿电路,从而提升了放大器的电流和功耗,限制了放大器带宽,同时降低了放大器速度,因此不能满足本设计中对于运放带宽和速度的要求。套筒式结构虽然具有较高的增益、较好频率特性及较低功耗,但是受到结构限制,其输出摆幅和共模输入范围小,不满足设计要求。折叠式共源共栅结构针对套筒结构输出摆幅小的缺点进行改进,通过增加电路支数,提高功耗,在提供较高的增益前提下,又满足了大带宽、高摆幅和高速的要求。通过对折叠共源共栅结构应用增益增强技术,可以在不影响信号带宽、压摆率和相位特性的情况下进一步提高电路直流增益。因此,针对本设计的特殊要求,选取了应用增益增强技术的折叠式共源共栅结构。

1.1 主运放电路

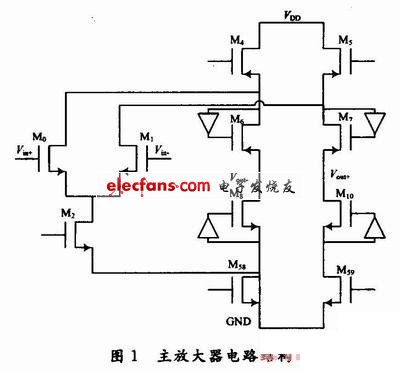

本文设计的折叠共源共栅运算放大器如图1所示。M0,M1为差分输入对管;M2为差分对管恒流源;M4,M5为电流源;M6,M7为共栅管;M8,M10,M58,M59为共源共栅电流源负载。由于NMOS管的载流子迁移率更高,采用NMOS管作差分输入级可提高运放增益和带宽。

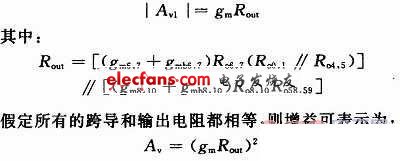

当无增益提高辅助运放时,主运放的小信号电压增益为:

可见,与基本的恒流源负载放大电路相比,输出节点的输出电阻增大gmRout倍,所以共源共栅结构的运算放大器能够提供高增益。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)