利用共源共栅电感可以提高共源共栅结构功率放大器的效率。这里提出一种采用共源共栅电感提高效率的5.25GHzWLAN的功率放大器的设计方案,使用CMOS工艺设计了两级全差分放大电路,在此基础上设计输入输出匹配网络,然后使用ADS软件进行整体仿真,结果表明在1.8V电源电压下,电路改进后与改进前相比较,用来表示功率放大器效率的功率附加效率(PAE)提高了两个百分比。最后给出了功放版图。

1 共源共栅电感的工作机理

本次功率放大器设计中使用到共源共栅(Cascode)结构,这种共源共栅管的源极存在着较大的寄生电容,这在本次5.25GHz功率放大器的设计中是不得不考虑的。由模拟电路知识可知:如果电路中有电容,那么电路上的信号就要对电容进行充放电。所以共源共栅管源极的寄生电容就要从电源汲取电流进行充放电,这样势必增加了额外的功耗,从而降低了功率放大器的效率。

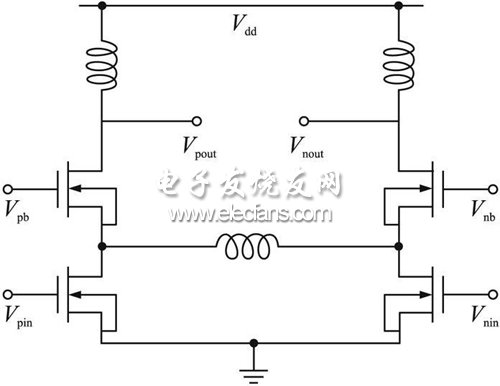

如果给这些寄生电容提供一种能量交换渠道,使其尽可能少地从电源处汲取电流,那么就会降低这些寄生电容对功率放大器效率的影响。根据对模拟电路的基本认识,不难想到可以引入电感,电感和寄生电容之间可以进行能量的交换,从而减少了寄生电容对电源处电流的依赖,也就减少了额外功耗,会在一定程度上提高功率放大器的效率。图1是上述思想的具体实现,中间的共源共栅电感是一个对称型电感,可以拆成两个电感量相同的电感,他们的电感量是该对称型电感的一半。加入输入信号后,电感与共源共栅管的源极寄生电容会发生谐振,进行能量的交换,这就降低了寄生电容充电时对电源处电流的依赖程度。

本次A类两级功率放大器设计,原理图中第一级加入了共源共栅电感,第二级并未添加,主要是从版图面积的角度考虑的,因为电感在芯片中所占用的面积比其他元件都要大很多。此外,在进行版图设计时,有意将原理图中一个共源共栅电感拆分成两个电感,这是为了提高电路结构的对称性,从而有利于功率放大器的整体性能,关于这一点,将在后面的版图设计中进行分析。

图1共源共栅电感的应用

2 功率放大器设计

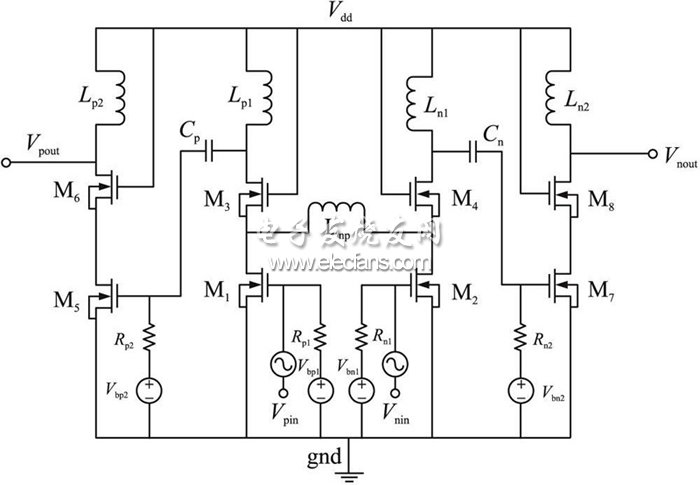

放大电路如图2所示,电路结构为差分形式,采取两级放大,分别为驱动级和输出级。驱动级采用差分的共源共栅(Cascode)结构,可以提供适当的电压增益;输出级也是差分的共源共栅结构,在提供一定的电压增益的同时,还提供输出功率,这种结构可以提高功放输出电压的摆幅,从而降低对MOS管最大电流能力的要求,提高功放的效率。两级之间采用的耦合电容Cp和Cn在提高隔离度的同时起到级间阻抗匹配的作用。电感Lp1、Lp2、Ln1、Ln2用作负载,电感Lnp用来抵消源极寄生电容对功放效率的影响,其中Lp1、Ln1和Lnp采用工艺库里的片上螺旋电感来实现,而Lp2和Ln2可以采用高Q值的键合线电感实现,这样可以有效提高功放的增益,当然只要工艺条件允许,在对增益要求不是很高的情况下,也可以采用工艺库里的片上螺旋电感来实现。单路输入信号经输入匹配网络由巴伦转换成两路信号Vpin和Vnin,放大后的两路信号Vpout和Vnout经输出匹配网络由巴伦转换成一路信号送至天线。其中,输入匹配采用共轭匹配以达到最大增益,输出匹配采用功率匹配以输出最大功率,都是以简单的LC匹配网络为实现形式,通过高频辅助设计软件ADS中的Smithchart来设计。

图2 两级A类放大电路结构示意图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)