OFweek垂直分层闸流体(VerTIcal Layered Thyristor;VLT),是Kilopass研发出的新型内存单元,能够显著降低动态随机存取内存(DRAM)的成本和复杂性。这是一种静态的内存单元,无需刷新 *** 作;兼容于现有晶圆厂的制造设备,也无需任何新的材料或工艺。

相较于一般的DRAM,VLT内存数组能节约高达45%的成本;这是因为它具有更小的VLT内存单元,以及驱动更长行与列的能力,使其得以大幅提升内存数组效率。然而,想要发挥VLT的优势,就必须在依据产业标准发展的成熟DRAM市场展开设计与制造,才能确保兼容于不同供应商的内存产品。

目前,基于VLT技术的内存已经具备与现有“第四代低功耗双倍数据速率”(LPDDR4)规格完全兼容的能力。VLT内存组(bank)可以模拟传统DRAM的bank,并兼容于其频率;在设计VLT电路时,设计者可以选择连接标准DDR控制器,或是成本较低的简化版控制器。如果使用标准控制器,由于不需要刷新,VLT内存将会忽略刷新序列。系统的其他部份则会将VLT DRAM视为通用DRAM,因而无需任何改变。

传统DRAM内存单元为了显示如何使用VLT内存单元构造LPDDR4内存,首先回顾一下传统DRAM以及LPDDR4的工作方式。熟悉DRAM者或许对其有所了解,但实际运用上还是有些微差异,在此先定义一些准则与术语以便于理解。

DRAM作业的许多方面取决于其电容储存单元。首先,电容的漏电特性导致了刷新的必要性;其次,储存单元的基本作业方式之一是读取,它会影响如何组织内存的其他方面。

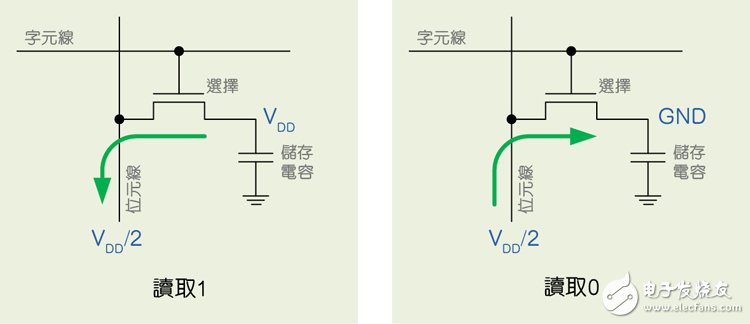

图1显示电容储存单元的原理图,左右图分别代表了读取1和读取0时。电路透过“电荷分配”(charge sharing)侦测内存位值。位线(bitline)首先被预充电到一个在0和1之间的电压值,然后透过打开读数晶体管来选择一个内存单元,使电荷可以在位线与内存单元间流动。如果位线电压高于内存单元,那么负电荷就会从内存单元流出到位在线;而如果位线的电压低于内存,那么负电荷就会从位线流进内存单元。

图1:传统电容式DRAM内存单元的电荷分配原理 (图中绿色箭头所示为电流,与负电荷流动的方向相反)

这种电荷转移改变了位在线的电压,透过感测与锁存得到最终读取数值。然而,在储存电容中失去或取得的电荷,改变了节点上原有的电荷,这意味着读取的过程是破坏性的。因此,在每一次读取之后,都必须透过回写 *** 作恢复内存单元中的电荷。

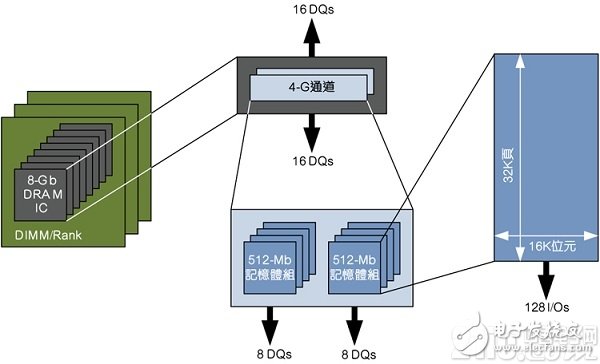

LPDDR4LPDDR4标准是第四代双倍数据速率(DDR) DRAM的低功耗版本标准,透过整体架构定义了个别内存芯片的高层级结构,以及如何安排双列直插式内存模块(DIMM)。

分析DRAM的方式一般有两种:理论上,剖析其实体细节;实际上,则着眼于其芯片数组特性。本文首先探讨第一种逻辑观点,因为所有的实体布局都必须分解为相同的逻辑结构,因而能够从中了解传统DRAM和LVT途径如何实现逻辑功能。

LPDDR4内存芯片拥有8Gb的储存容量,通常由两个4Gb的独立通道共同组成。每信道拥有8个内存组,每一内存组包括32K储存页(page),每页有16K位,而使内存组的总容量达到512Mb。

图2:典型的DRAM架构和层级

一个完整的LPDDR4内存芯片包括两个高层级单元:内存数组和DDR接口。有些部份的 *** 作会影响到内存数组;另一部份则会影响接口。DDR接口可以同时与内存数组以及外部系统进行通讯。

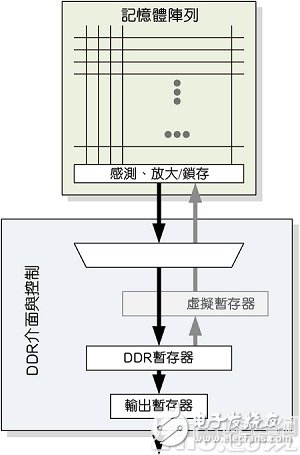

图3:LPDDR4的逻辑组织架构,图中将储存数组和DDR接口分开。(箭头代表一次读取 *** 作以及回写)

图3说明了这种关系,即DDR缓存器作为外部系统和内存数组之间的主接口。而在读取数据时,数组数据会先被加载DDR缓存器中;进行写入作业时,所需的数据会先从外部写入缓存器中。

由于读取传统DRAM数组内容可能破坏原有数据,每一次读取后都必须进行回写作业,以恢复原有值。在进行读取后,DDR缓存器的内容被复制到“隐藏缓存器”(Shadow Register)中。当外部系统读取DDR缓存器中的数据时,隐藏缓存器负责将数据回写到所选页,以恢复原有数值。同样地,当写入数据时,DDR缓存器的数据会被传输到隐藏缓存器中等待写入;而在执行写入作业时,DDR缓存器就可以加载新的数据。

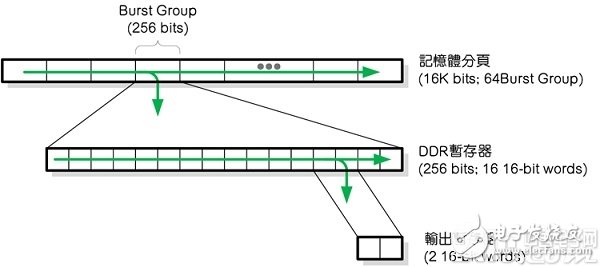

读取内存分页数据涉及一连串的活动,类似于两个巢式的软件DO回路(Do loop)。每一分页内存被分成由许多256字节成、成批(burst)读取的内存群组,因此,一组16K位分页就有64个burst内存群组,依序读取完整的内存页,这类似于外部DO回路。

每个突发传输组被加载256位的DDR缓存器中,该缓存器被分为16个16位字,并依序读取其内容,为每一个频率边缘提供每一个16位字。这种 *** 作方式则如同内部DO回路。

每一行的地址(RAS)负责选择分页。同时,每一列的地址(CAS)选择突发传输组,并设置从DDR缓存器中开始读取的字符,因而不必从DDR缓存器的左侧开始读取。

值得注意的是,在隐藏缓存器执行回写、读取或写入DDR缓存器中原先加载数据的同时,DDR缓存器已经开始从储存数组中读取数据或从外部加载所写数据了。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)