0 引言

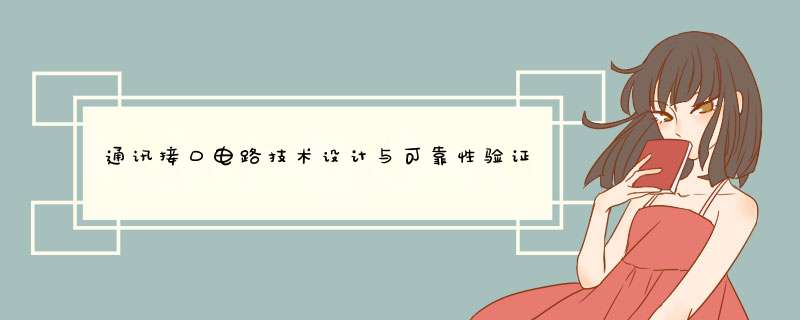

通讯接口电路主要用于完成前端综合处理机和后端的发送控制系统(简称发控系统)、飞机控制系统(简称飞控系统)等的信号交联。综合处理机输出的目标信息经过电气匹配后送到单片机,单片机对其进行解析后,按照一定的帧协议将目标信息转发给发控系统,并将目标信息中包含的干缆高度信号进行数模转换及滤波放大后送至飞控系统和悬停器。

1 电路组成与工作原理

1.1 电路组成

根据通讯接口电路的主要功能,设计该电路的组成框图如图1所示。

1.2 电源电路

接线盒系统由一路28V直流电源供电,在此利用稳压芯片分别转换得到以下三路电源:

1)运算放大器电源:一路15.0V;2)MCU电源:两路3.3V,分别为供数字电路和模拟电路使用;3)其他芯片电源:一路5.0V。

1.3 控制电路

通讯接口电路的控制单元MCU在进行数据处理时,除了需要根据综合处理机与接线盒接口控制协议对数字信号进行解析,还需要完成对干缆高度数据信号的D/A转换,要求高度分辨率小于0.1m。

基于硬件资源需求,结合低功耗、集成化、开发周期等因素,该控制电路选用了MSP430系列的单片机。该单片机具有两个串口并内置12位DA转换器,在低功耗、可靠性方面表现出色,满足设计需求。

我们选择DAC12的基准电压为2.5V,理论上其电压分辨率为2.5/4096=0.6mV,实际上由于器件本身的误差加上电路噪声的影响,其有效位可能降低为10位,则电压分辨率随之降低为2.5V/1024=2.4mV。

由于DAC12输出的直流电压模拟量的范围为0~2.5V,而飞控系统和悬停器要求的电压输入范围为0~12V,因此需要对DAC12的输出电压进行比例放大,增益系数计算如下:G=Int(12/2.5)=5。同时,由于电压放大的缘故,在飞控系统的输入端,电压分辨率相应降至2.4×5= 12mV。此外,已知电压与干缆高度之间的比例关系为80mV/m,据此计算出高度分辨率为12/80=0.15(mV/m),满足小于0.2m的设计要求。

1.4 电气匹配

在电路设计中,由于综合处理机、MCU和与发控系统之间的通讯信号的输入/输出逻辑不协调,需要首先解决两种电平的转换问题,我们在此采用的电气匹配芯片为ADM485。

对于不出户外的422端口,我们采取了单向的保护措施,设计了由TVS管P6KE6.8CA和WE-SL2型共模电感组成的接口保护电路。当TVS管两端经受瞬间的高能量冲击时,它以极高的速度使其阻抗骤然降低,同时吸收一个大电流,将其两端间的电压箝位在一个预定的数值上,从而确保后面的电路元件免受瞬态高能量的冲击而损坏。

2 通讯协议

为保证综合处理机、接口电路MCU和与发控系统之间能有效、可靠地进行通信,我们对数据的格式、顺序和速率,数据传输的确认和接收,差错检测,重传控制和询问等 *** 作做出了约定,形成了通讯协议。

2.1 综合处理机与接线盒通讯标准

综合处理机通过一个串行通讯链和接线盒进行交联。通讯标准如下:电气标准:EIA RS-422;信号:RxD+、RxD-、TxD+、TxD-、GND;字节:起始位1位、数据位8位、停止位1位、无校验位;速率:9.6kb/s;方式:异步。

2.2 综合处理机与接线盒的数据包格式

综合处理机向接线盒发送固定格式、固定数据周期的数据包,数据内容包括目标信息、干缆高度、声纳有效标识和状态查询命令标识。当接线盒接收到的数据包状态查询命令标识为有效时,接线盒向综合处理机发回状态信息数据。

2.3 接线盒与发控系统通讯数据协议

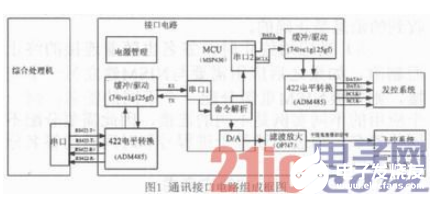

接线盒接口电路向发控系统输出两路信号,一路为串行数据信号DATA和/DATA(差分信号),另一路为时钟信号BCLK和/BCLK,两路均为差分信号。其格式如下:

据此,可读出目标距离、目标方位、目标编码,与发控系统显示器上的目标距离、方位及 *** 纵台上设置的目标标号比较,就可知其正确性。

3 软件设计

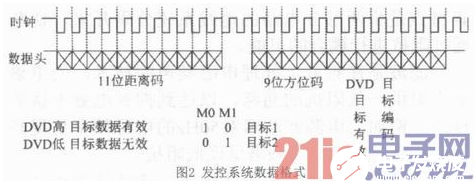

国内普及的MSP4307开发软件种类不多,我们以用户相对较多的IAR EW430作为开发环境。主函数流程图如图3所示,其中GO信号是一路标志信号,当单片机指定的GO信号引脚置高时,即向发控系统确认前级电路工作正常。

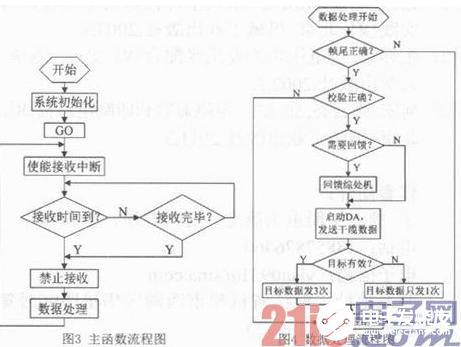

子函数的功能分为初始化、延时、串口接收中断、定时中断、数据处理等,其中数据处理的过程相对复杂,包括根据协议对发控系统目标数据进行编码,生成25位数据块,此外还要启动DA,发送干缆高度数据等等,数据处理流程图如图4所示。

此外,我们采用定时器中断方式产生发控系统目标数据发送的时钟周期,在一个时钟周期内,由于高、低电平的持续时间均要求精确到0.01 μs,用C语言的延时语句难以控制,而用定时器中断方式却能良好地实现,只要当计数完成时反复改变电平高低,就能产生精确的数据时钟。

4 电磁兼容性设计

电磁兼容性设计的关键技术是对电磁干扰源的研究,除了从电磁干扰源产生的机理着手降低其生产电磁噪声的电平外,还需广泛应用屏蔽、滤波和接地技术。

通讯接口电路当中,屏蔽主要运用光电耦合器等器件来切断电磁噪声以传导形式的传播途径,其特点是将两部分电路的地线系统分隔开来,切断通过阻抗进行耦合的可能。

滤波是在频域上处理电磁噪声的技术,为电磁噪声提供一低阻抗的通路,以达到抑制电磁干扰的目的。例如,电源滤波器对50Hz的电源频率呈现高阻抗,而对电磁噪声频谱呈现低阻抗。

接地包括接地、信号接地等,接地体的设计、地线的布置、接地线在各种不同频率下的阻抗等不仅涉及产品或系统的电气安全,而且关联电磁兼容和其测量技术。

5 小结

文章设计的通讯接口电路已经顺利通过了联调试验,其技术指标满足设计要求,有效性和可靠性得到了验证。其设计方法具有较强的实用性和参考应用价值。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)