近年来,软件无线电已经成为通信领域一个新的发展方向,数字下变频技术(Digital Down Converter-DDC)是软件无线电的核心技术之一,也是计算量最大的部分。基于FPGA的DDC设计一般采用CIC、HB、FIR级联的形式组成。同时,由于CIC滤波器的通带性能实在太差,所以中间还要加上一级PFIR滤波器以平滑滤波器的通带性能。而众所周知用FPGA从事算法的开发是一件难度比较大的工作,而Xilinx公司开发的System Generator工具为算法的快速开发及仿真带来了巨大的方便。本文首先对CIC、HB、FIR滤波器的原理及设计作了简单的说明,最后用Matlab结合System generator对本文所设计的DDC滤波器作了一个仿真。

1 总体结构设计

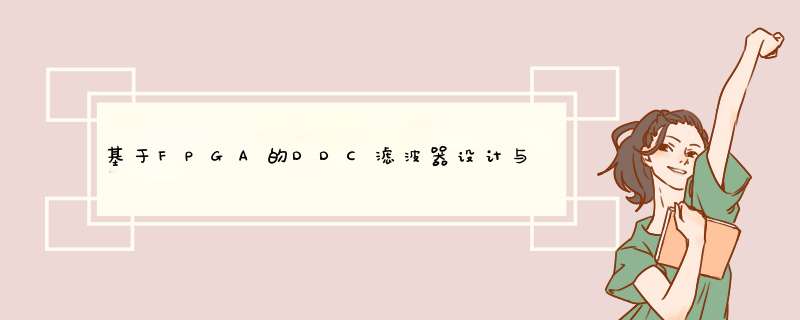

数字下变频技术作为数字信号处理中的一个关键技术,它通常由以下儿部分组成。首先,CIC滤波器,它实现简单而且能实现较大的下抽率。其次,由于CIC滤波器带内平坦性能太差,因此在CIC滤波器之后一般要加上PFIR来平滑带内平坦度。最后,由于CIC滤波器的抽取因子小宜取得过大,冈此还要用HB滤波器的级联来进一步增加抽取率。下面本文以如何设计一个原信号采样率为72 MHz的、有效信号带宽为2.05 MHz的、下抽率为14的、主旁瓣衰减80 dB以上的、通带平坦度小于0.2 dB的下抽滤波器为例说明下抽滤波器的设计。

实际中常用的DDC的实现框图如图1所示。

2 CIC滤波器设计

CIC滤波器是近年来在下变频中用得最多的一种技术,CIC滤波器在多速率信号处理中具有特别重要的位置,它可以充当内插滤波器,也可以充当抽取滤波器,主要取决于积分器和梳状滤波器的连接顺序。由于CIC(级联积分梳状)滤波器不需要乘法运算和存储系数,因此实现非常简单,在采样率变换过程中经常使用CIC滤波器进行数字滤波。

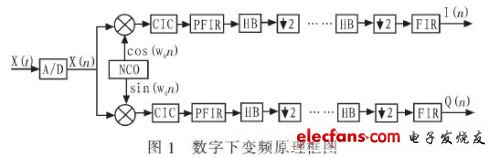

考虑到CIC滤波器的除数及抽取因子不宜取得过大,所以实际巾的下抽滤波器一般都是采用CI协同HB来完成下抽的任务。比如这里我们要下抽14,一般的做法是先用CIC下抽7然后用HB下抽2 如果这时一级HB仍然不满足要求的话,我们可以通过适当增加HB的级联数目来完成下抽。例如,如果要下抽28,那么可以先下抽7,然后通过两级HB来完成下抽4,进而达到下抽28的目的。

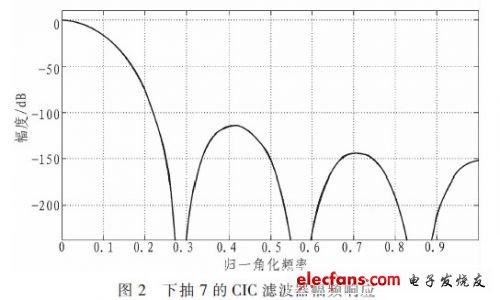

在MATLAB中通过设置下抽因子,需要的通带截止频率等参数可以方便的设计出想要的CIC滤波器。下图为本次设计中设计出的CIC滤波器的幅频响应。

通过将其通带细节图放大,可以发现在2.05 MHz处通带的衰减为4.508 dB。

3 PFIR滤波器设计

PFIR滤波器的设计目标是在满足通带波纹和过渡带宽尽可能窄的同时使得阻带衰减尽可能大,PFIR的阶数越高,PFIR滤波器的通带波纹,过渡带宽,阻带衰减等特性就越好。

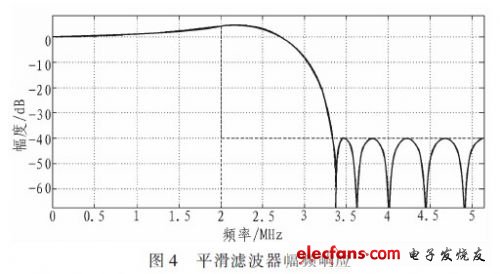

PFIR存在的意义是它能够改善CIC滤波器带内平坦度较差的问题,因此,其带内的幅频响应的走势和CIC正好相反,从而在一定程度上平滑CIC滤波器通带内衰减的趋势。在设计好了上一级CIC滤波器的基础上,通过输入已经完成的上级滤波器参数在MATLAB中可以自动生成与其互补的PFIR滤波器,它的幅频响应如图4所示。

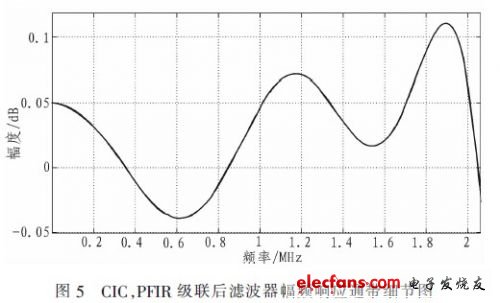

通过将这里设计的PFIR滤波器与上节设计的CIC滤波器进行级联,级联后的滤波器的幅频响应较之于之前设计的CIC滤波器其通带性能有了很大的提高,级联前的CIC滤波器的通带波纹为4.508 dB,而级联后仅为0.11 dB将其通带细节图如图5所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)