摘要:二维离散余弦(DCT)在H.264视频编码中承担者信号从时域到频域变换的作用。在现场可编程逻辑门阵列(FPGA)上设计了高效的采用流水线结构的H.264 DCT硬件电路。首先,把二维4×4 DCT变换转换成二次一维DCT变换;其次,DCT变换之间加一个两端口的RAM,以实现数列的转置;最后,在顶层设计一个有限状态机控制整个流程。该设计采用较少的资源实现了较好的功能,获得了可靠的实验结果。

关键词:二维离散余弦变换;FPGA;H.264;DCT

引言

目前,基于分块DCT的编码技术已成为图像/视频编码国际标准的核心技术,一方面是因为DCT具有良好的去相关性和能量压缩性,另一方面是因为DCT具有快速实现算法。随着数字多媒体技术的快速发展,H.264视频压缩标准在多个领域得到了广泛的应用。然而,在当前有限的网络带宽、FPGA有限的资源以及要求更高压缩速率情况下,对二维离散余弦变换(DCT)提出了更高的要求。H.264对图像或预测残差采用了4×4整数离散余弦变换技术,避免了以往标准中使用的通用8×8离散余弦变换、逆变换经常出现的失配问题。

1 H.264的整数DCT变换

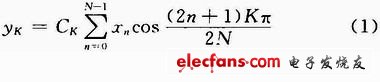

一维N点离散余弦变挽(DCT)可以表示为:

式中:xn是输入时域序列中第n项;yK是输出频域序列中的第K项;系数CK定义如下:

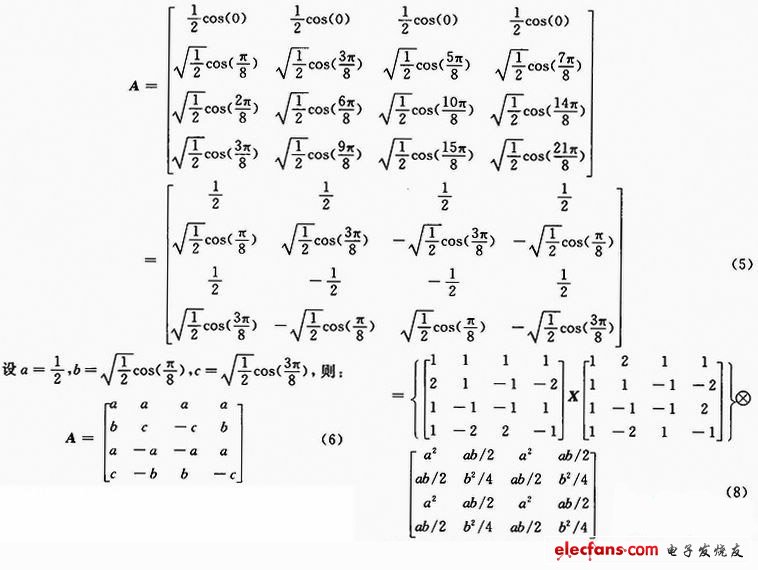

H.264对4×4图像块进行 *** 作,则相应的4×4DCT变换矩阵A为:

![]()

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)