AT45DB081B在数据采集系统中的应用

在信号采集系统中,往往需要对多种数据波形进行存储、转移或比较,这就要求系统能方便地访问、传输波形数据。FLASH存储器以其体积小、容量大、可随机访问的特点,在系统中得到了很好的应用。本文从实际应用角度出发,简单介绍了FLASH存储器AT45DB081在数据采集系统中的软/硬件设计思路和设计要点。

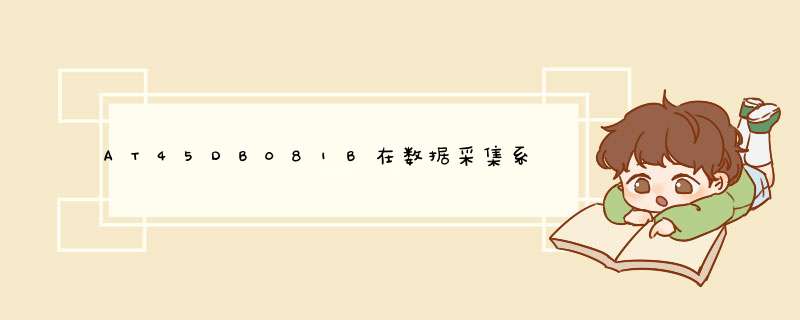

1 系统设计

本系统的整个数据存储系统可以分为数据缓冲模块、控制单元和FLASH存储模块三个部分,其系统结构框图如图1所示。图中数据缓冲模块负责对端口数据进行缓冲,以满足FLASH存储器的传输要求。控制单元可按照FLASH存储器的控制要求,对FLASH的读写、擦除 *** 作进行控制。在存储开始后,FLASH的控制单元将数据缓冲模块中的数据存入相应的FLASH存储器中,直到计数器计到设定的数值为止。在本系统中,一次存储只对一组数据进行 *** 作,这样可以保证各组数据之间不出现覆盖,以增加存储的有效性和可靠性。

2 FLASH芯片AT45DB081B

AT45DB08lB是Atmel公司推出的串行Flash存储器,该芯片采用串行外围接口,具有体积小、容量小、功耗低和硬件接口简单的特点,易于构成微型低功耗测量系统。AT45DB081B的最大时钟频率可达20MHz,它支持页和块(1块=8页)擦除功能,有4096页,每页264B容量,并具有两个264B缓冲区。

AT45DB081B的相关 *** 作包括读主存储页、主存储页数据拷贝到缓冲区、主存储页与缓冲区数据比较、缓冲区数据写入主存储页、页擦除、块擦除、页编程和页重写读、缓冲区、写缓冲区和读状态寄存器等。其中缓冲区数据写入主存储页的 *** 作中又包括写前擦除和边写边擦。

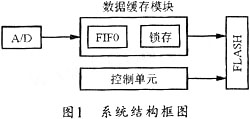

AT45DB081B支持SPI 0和SPI 3两种传输方式,其时序图分别如图2所示。

3 硬件电路

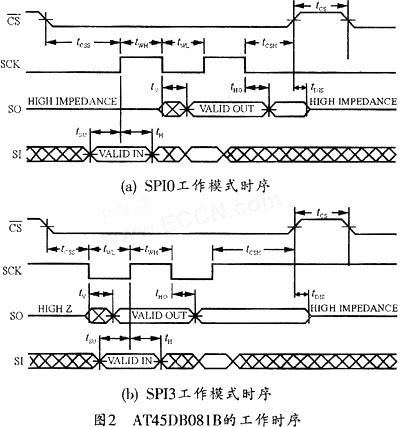

本系统选用PHILIPS公司的P89LV51RD2BN微控制器进行控制。P89LV51RD2BN是一款80C5l微控制器,包含64kB Flash和1024字节的数据RAM,它的典型特性是×2方式选项。设计者可通过该特性来选择以传统的80C51时钟频率(每个机器周期包含12个时钟)或×2方式(每个机器周期包含6个时钟)的时钟频率运行,其中,选择×2方式可在相同时钟频率下获得2倍的吞吐量。该特性可将时钟频率减半而保持特性不变,并可极大地降低EMI。P89LV51RD2BN与AT45DB081B的连接如图3所示。为保证其可靠性,在上电后,应对FLASH进行复位,然后通过RDY口确定芯片是否处于忙状态,之后再进行相应的 *** 作。

需要注意的是,RDY的上拉电阻不能省去,以保证输出的准确。

4 系统软件设计

波形数据可以按页存储,在进行数据 *** 作时,可以按页读取和处理,这样相对会更加方便。按每一次波形1 KB的数据量来计算。若每4页存储一个波形数据,理论上则可以存储1024个波形。

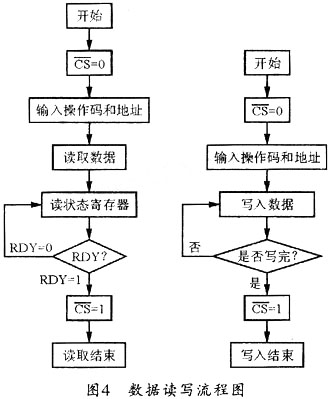

数据可在控制单元的控制下进行缓冲锁存。 *** 作时,可以先将264 Bytes的数据写入buffer中,计数器计为1。再将buffer中的数据送入内部存储单元,并重复以上 *** 作,当计数器计到4时,即可完成一个波形数据的存储。读 *** 作则反之,即将数据先送入buffer,再由buffer向外部传输,且仍以计数4次为一 *** 作周期。每次读写流程如图4所示。

5 结束语

将串行FLASH存储芯片AT45DB081B应用于数据采集系统可使电路设计简单化。它占用系统资源少且性价比较高。目前,该系统已应用于电缆故障检测中,效果很好,而且易于编程。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)