在高速数字电路中,CPU的功耗往往随着主频的提升而增大,如果PCB Layout不当,则可能会引起CPU工作不稳定,本人就曾经遇到过。Marvell 88F6282 CPU运行在2GHz主频时,进行Memory Test测试,发现CPU常常不工作,而且每次不工作的时间点没什么规律,但是当CPU降频到1.6GHz运行时,这种现象不会发生。

进行以下分析

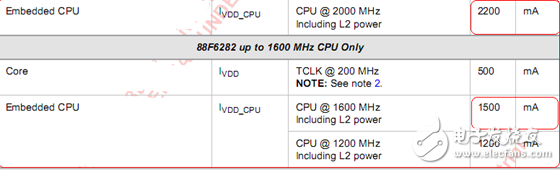

Memory Test是验证CPU和DDR在大负载情形下能否正常工作的一种方式,当系统运行在1.6GHz的时候,是正常的,说明CPU和DDR物理连线上是OK的,当升级到2GHz后会出现不工作,这种现象有两种原因:一种是时序上尤其是Set-up TIme和Hold TIme大于Margin,在1.6GHz时,因为频率相对来说低点,也就是时钟周期相对来说长点,所以时序上可能能满足CPU对访问DDR的要求,但是升级到2GHz后,由于时钟周期变短了,很有可能导致时序不能满足要求,导致CPU访问DDR时出现读写错误。为了验证这种想法,我们测试了2GHz时CPU访问DDR的时序,结果显示是时序满足要求的。另一种可能是CPU供电不足,因为,从Marvell 88F6282的Datasheet上看,CPU工作在2GHz时比工作在1.6GHz时电流消耗增加了700mA。

但是打开我们的PCB,我们发现VCC_CPU是通过第三层的Power层经过过孔来提供电流路径的,检查发现有效的电流路径宽度是40mil左右,根据经验公式,40mil线宽在表层可以走1A的电流来算,这个线宽是不能满足CPU供电要求。

Top层VCC_CPU网络

Power层VCC_CPU网络

解决方案

比较简单的方法是从VCC_CPU电源处走一个飞线到CPU供电引脚处的电容。最终的方法是改Layout,使VCC_CPU电源层线宽最小处为80mil,改版后,这个问题就没有再出现了。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)