随着微电子制造业的发展,制作高速、高集成度的CMOS电路已迫在眉睫。在短沟道CMOS电路中由于不匹配性引起的特性变化可能会限制器件尺寸的减小而影响工艺水平的发展,这样不匹配性的消除就显得更重要。

1 差分放大器性能

差分放大器的目的是抑制共模输出,增大差模输出。期望差模输出电压随差模输入电压的变化而成比例变化。任意信号中的共模输入部分在电路中必须受到抑制。在理想对称的差分放大器中,每边的输出值都等于另外一边的输出值。当Vi1=-Vi2时,有Vo1=-Vo2,此时放大器是理想对称的。换言之,当输入是理想的差模电压(Vic=0)时,输出也是纯粹的差模形式的电压(Voc=0),因此Adm-cm=0。类似的,当只输入共模电压(Vid=0)时,Acm-dm=0。但是,即使在理想对称的差分放大器中,也不可能做到Acm=0。何况,即使标称相同的器件也会因为制造工艺的原因,存在有限的不匹配(失配)。因此非理想差分放大器本身还存在不匹配现象。

差分放大器性能的一个重要方面就是所能检测到的最小直流和交流差模电压。放大器的不匹配效应和温漂都在输出端产生了难以区分的直流差模电压。同样,不匹配效应和温漂会使非零的共模输入一差模输出增益非零的差模输入一共模输出增益增大。非零的Acm-dm对于放大器尤其重要,因为它将共模输入电压转换为差模输出电压,但在下一级输入时,却被当作差模电压信号。

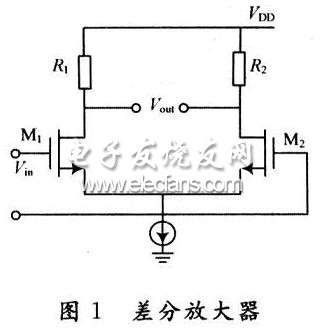

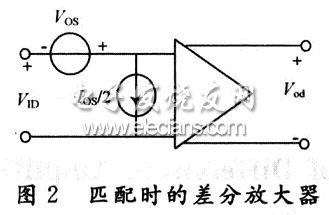

如图1所示,当Vin=0,且完全对称,Vout=0,但在失配存在的情况下,Vout≠0。对于差分放大器来说,不匹配效应对直流性能的影响主要在两个方面:输人失调电压和输入失调电流,这两个参量描述了差分放大器中直流性能的一些输入参考效应。如图2所示,一个匹配的放大器的直流特性和一个失调电压源串联在输入端、失调电流源并联在输入端的时理想放大器的直流特性完全一致。只有当这两个参量都存在的情况下,失调模型才是正确的。

2 工艺消除失配

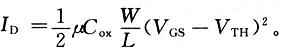

将处在饱和区的MOS管的特性表述为:

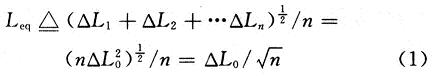

1/2μCoxW/L(VGS-VTH)2。对于两个标称相同的晶体管,μ,Cox,W,L以及VTH之间的失配导致了漏极电流的失配(VGS固定)或栅源电压的失配(漏极电流固定)。直观上可以认为,随着W与L的增加,他们的相对失配,△W/W与△L/L会分别减小,也就是越大的器件表现出越小的失配。一个更重要的观察结果是,随着晶体管面积(W/L)的增加,所有的失配都减小。例如,增大W会使△W/W与△L/L都减小。这是因为随着WL,的增加,随机变化经历更大的“求平均”过程,因此其幅值下降了。对于图3所示的情况,有△L2<△L1。这是因为,如果该器件被看成许多小晶体管的并联,如图3所示,若每一个宽度为W0,那么可以得出等效长度为:

式中:△L0是宽为W0的晶体管长度变化的统计值。等式表明,对于给定的W0,随着n的增加,Leq的变化减小,如图4所示。

上述结论也可以扩展到其他器件参数。例如,假定:器件面积增加,μCox与VTH有更小的失配。如图5所示,理由是,大尺寸晶体管可以分解为宽长分别为W0和L0小单元晶体管的串并联。其中,每个单元都呈现出(μCox)j与VTHj。对于给定的W0与L0,μCox与VTH经历更大的平均过程,致使大尺寸晶体管之间的失配更小。

3 版图方法减少失配

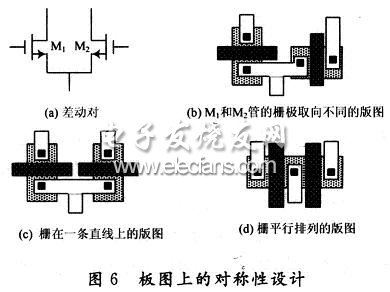

针对电路设计中,特别是全差动电路中的不对称而产生的电路失调,尽管有些失配是不可避免的,但是在版图设计中,可通过器件对称设计,使晶体管方面优化,对所关心的器件及周围环境进行对称性设计,尽量减少因工艺制造原理而引起的失配。

如图6(a)所示,如果两个MOS管按图6(b)那样沿不同方法放置,由于在光刻及圆片加工的许多步骤中沿不同轴向的特性大不一样,就会产生很大失配。因而图6(c)和(d)的方案更合理一些。这两者的选择是由一种称作“栅阴影”的细微效应决定的。

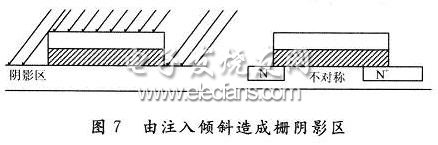

如图7(b)所示,为了避免沟道效应,通常在源一漏离子注入时把注入方向(或圆片方向)倾斜7°左右,这样栅极多晶硅就会阻挡一部份离子,形成阴影区。结果,在源区或漏区就有一条窄区,它接收的注入较小,因而在注入退火之后,使源区和漏区边缘的扩散产生了细微的不对称。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)