很多FPGA设计中都会涉及到多个时钟,使用器件内部的PLL或者DLL会使得多个时钟的管理变得更加容易。但是当多个时钟都是用PLL/DLL产生时,他们的系统复位信号如何设计才更加稳定呢?

在上一章《FPGA——复位设计》的内容里提出了异步复位、同步释放的方法,那么在系统复位后、PLL时钟输出前,即系统的工作时钟不确定的情况下,应该怎么考虑这个复位问题呢?

下面就解释一下所用的方法。

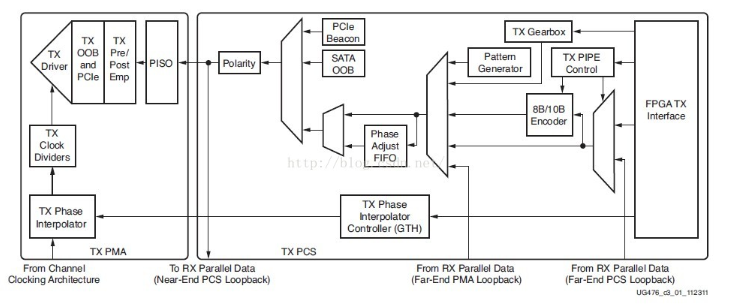

如下图,就是所用的RTL电路图。先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。PLL的输出locked信号在PLL有效输出前一直时低电平,PLL输出稳定有效之后才会拉高该信号,所以这里就把前面提到的FPGA外部输入复位信号rst_n和这个locked信号相与作为整个系统的复位信号,当然了,这个复位信号也需要让合适的PLL输出时钟异步复位、同步释放处理一下。也就是说,为了达到可靠稳定的复位信号,该设计中对复位信号进行了两次处理,分别是在PLL输出前和PLL输出后。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)