一般而言,用来驱动现今高分辨率类比/数码转换器的电源都是拥有数百欧姆或以上的AC或DC负载。因此,一个具备有高输入阻抗(数百万欧姆)和低输出阻抗的运算放大器便成为ADC驱动器输入的最佳选择。ADC驱动器可作为缓冲器和低通滤波器之应用,以减低系统的整体杂讯。

随着讯号在电路板的布线和冗长电缆上传送,系统杂讯会积聚在讯号里,而一个差动ADC会拒绝任何看来像共模电压的讯号杂讯。相比起单端的讯号,采用差动讯号有好几个优点。首先,差动讯号可将ADC的动态范围增大一倍。其次,它可提供更佳的谐波失真效能。现今有几个方法可从一个双重运算放大器配置产生出差动讯号。其中一种方法是采用单端/差动转换技术,而另一种则需动用差动输入源。为了利用完全的ADC的动态范围,ADC的输入必须被驱动至满刻度的输入电压。

本文将会讨论三种不同的ADC驱动器架构:单到单、单端到差动和差动到差动。主要目的是希望能扼要地提供一切用ADC介接高效能运算放大器的资料。

讯号路径的必要组件

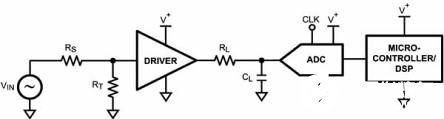

以下会把讯号路径中的类比前端设计之几个组成部份一起讨论。典型讯号路径的类比前端包括有一个用来驱动ADC的运算放大器、一个RC滤波器、ADC和微控制器或数码讯号处理器(DSP)。

图1:典型讯号路径的类比前端方块图

现实世界中的输入源会带有不理想的阻抗,因此需依赖一个很低输出阻抗的缓冲放大器来驱动ADC的输入。然而,外置的RL-CL滤波器会作用为一个抗叠频滤波器,以帮助减低ADC驱动器的杂讯频宽,以及缓冲由ADC取样和保持电路所引致的充电瞬时。为了尽量减低输入电压的跌降,外置的并列电容(CL)必须比ADC的内置输入电容大10倍,而同时外置的串行电容(RL)亦必须够大以固定发生在运算放大器输出的相位延迟,从而维持电路的稳定性。对于大部份的应用而言,在运算放大器输出和ADC输入之间用一个串行隔离电阻来连接,都可以带来益处,因为这个串行电阻可有助限制运算放大器的输出电流,而为这个串行电阻选定数值是一项非常重要的工作。

一个比较高的电阻值将会增加运算放大器的负载阻抗,从而改善运算放大器的整体谐波失真(THD)效能。可是,ADC通常都较喜欢以一个低阻抗的源来驱动。因此,必须为这个串行电阻找出最佳的数值,才能一同为运算放大器和ADC带来最佳的THD、SNR和SFDR效能。当把ADC连接到一个运算放大器时,最重要是了解将会影响到效能的规格。现今的ADC规格,例如是THD、SNR、设置时间和SFDR等,它们均对滤波、测量、视频和重现应用很关键。高效能运算放大器的设置时间、THD和杂讯效能必须比被驱动的ADC的效能更好,以确保系统的精确度以及将错误减至最低或甚至消除。

在本文中, LMH6611或LMH6618单一运算放大器会被用来驱动单通道的ADC121S101 类比/数码转换器,而另一方面,LMH6612或LMH6619双重运算放大器会被用来驱动差动输入的ADC121S625或ADC121S705类比/数码转换器。这些放大器的应用范围相当广泛,特别适用于要求高速、低供电电流、低杂讯,以及需要驱动复杂ADC和视频负载的应用。

运算放大器和ADC的重要规格

在现实中,有些系统应用会要求低THD、低SFDR和宽阔动态范围(SNR),而另一些则可能要求高SNR,并且可能会牺牲THD和SFDR的效能来换取更佳的杂讯效能。

对于运算放大器和ADC而言,杂讯都是一项很重要的规格。这里有三个主要影响ADC整体效能的杂讯来源:量化杂讯--是由ADC本身所产生的杂讯(尤其在较高的频率下),以及由应用电路所产生的杂讯。输入源的阻抗可影响运算放大器的杂讯效能。理论上,ADC的讯号与杂讯的比例(SNR)可用下列算式计算出来:

![]()

算式中的N是ADC的分辨率。例如根据这条算式,一个12位的ADC便拥有74dB的SNR。可是,实际的SNR数值会大约是72dB。为获得更佳的SNR,ADC驱动器杂讯应该愈小愈好。LMH6611/LMH6612/LMH6618/LMH6619的低电压杂讯仅为10 nV/ 。

运算放大器和ADC的整体设置时间必须在1 LSB之内,而LMH6618/LMH6619和LMH6611/LMH6612的0.01%设置时间分别为120ns和100ns。

此外,ADC驱动器的THD必须低于ADC。LMH6618/LMH6619在2VPP输出和100 KHz输入频率时的SFDR为100dBc,而LMH6611/LMH6612在2VPP输出和1 MHz 输入频率时的SFDR则为90dBc。

讯号/杂讯比和失真(SINAD)是一个参数,它结合了SNR和THD这两个规格。SINAD是指输出讯号的RMS值与所有其它低于时钟频率一半的光谱成份之RMS值之比例,这包括谐波但不包括DC,以及可凭下列算式从SNR和THR中计算出来:

由于SINAD是将输入频率与所有不良频率成份作比较,所以它其实是ADC动态效能的一个整体性测量。以下的部份将会详细讨论三种不同的ADC驱动器架构。

1. 单到单ADC驱动器

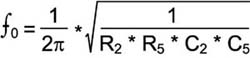

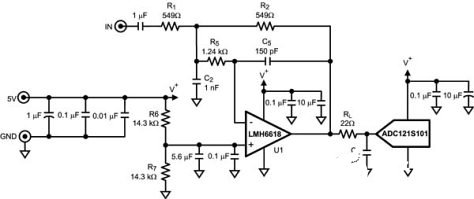

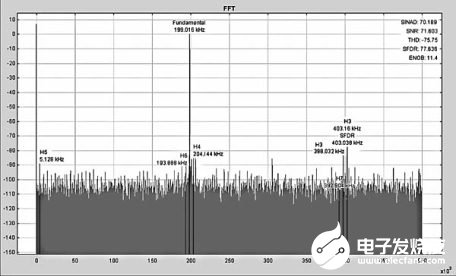

这个架构有一个单端式输入源接驳到运算放大器的输入,然后此运算放大器的单端式输出会再接驳到ADC的单端式输入。仅仅10 nV/ 的低杂讯和130 MHz的宽阔频宽促使LMH6618成为驱动12位ADC121S101 500KSPS至1MSPS 类比/数码转换器的首选,这个ADC拥有一个具备内置取样和保持电路的逐次逼近架构(successive approximaTIon architecture)。图2所示为一个驱动ADC121S101的LMH6618之原理图,所用的是具备有增益-1(反相)的二阶多重反馈配置。图中的反相配置比起非反相的为佳,原因是反相配置可提供更多的线性输出回应。表1列出LMH6611或LMH6618与ADC121S101组合后的效能资料。图3表示出在f = 200 KHz时的LMH6611和ADC121S101组合之FET绘图。ADC驱动器的500 KHz截止频率可从下列算式计算出来:

运算放大器的增益由下列算式设定:

![]()

图2:单到单ADC驱动器

图3:单到单ADC驱动器的FET绘图

表1:LMH6611/LMH6618与ADC121S101组合后的效能

2. 单端到差动ADC驱动器

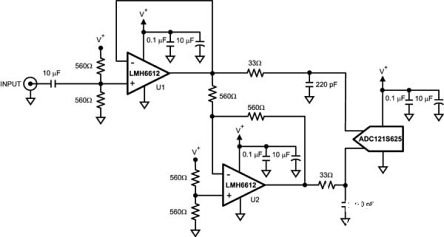

图4中的单端到差动ADC驱动器采用了LMH6612双重运算放大器来缓冲一个单端源,以便驱动一个具备有差动输入的ADC。其中一个运算放大器会被配置成一个单位增益缓冲器,并负责驱动运算放大器U2的反相(IN-)输入和ADC121S625的非反相(IN+)输入。U2把输入讯号倒向并驱动ADC121S625的反相输入。U2的增益配置为+2,因此可在无需牺牲THD效能下减低杂讯。至于2.5V的共模电压会同时设立在两个运算放大器U1和U2的非反相输入。

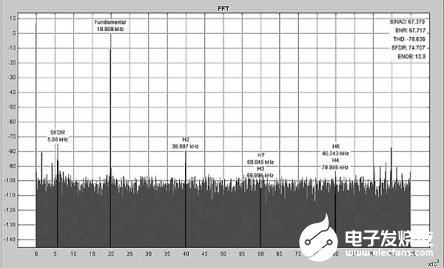

当0至VREF的单端输入讯号被AC耦合到运算放大器的非反相终端时,以及当每一个运算放大器的非反相终端在中标量2.5V下被偏压时,这种配置便可产生2.5Vpp的差动输出讯号。此外,两个输出RC抗叠频滤波器会同时使用在U1和U2的输出与ADC121S625的输入之间,以减轻来自输入源的不良高频杂讯之影响。每一个RC滤波器均具备有约22 MHz.的截止频率。图5表示出在f = 20 KHz时LMH6612和ADC121S625组合的FET绘图。

图4:单端到差动ADC驱动器

图5:单端到差动ADC驱动器的FET绘图

表2:LMH6612/LMH6619与ADC121S625两个组合的效能资料

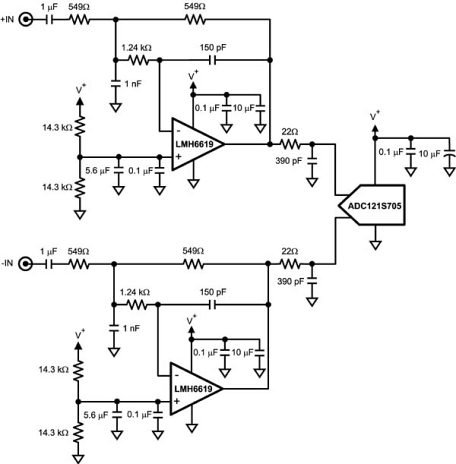

3. 差动到差动ADC驱动器

LMH6619双重运算放大器可以被配置成一个差动到差动的ADC驱动器,以便用来将一个差动源缓冲到一个差动输入ADC,正如图6所示。该差动到差动ADC驱动器可用两个单到单ADC驱动器组成。这些驱动器的每一个输出会接驳到差动ADC的个别输入。在这里每一个单到单ADC驱动器都采用相同的组件,并且配置成增益-1(反相)。

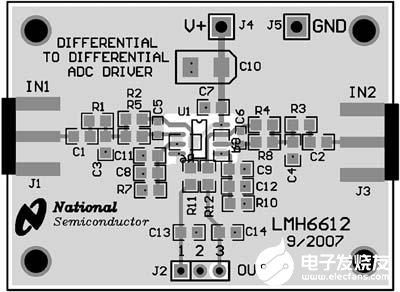

图6:差动到差动ADC驱动器

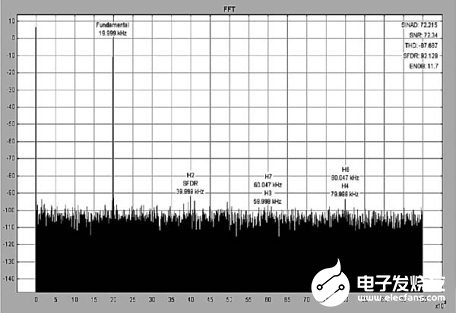

下表分别总结出LMH6612和LMH6619与ADC121S625和ADC121S705这四个组合的效能。表中同时包括有LMH6612和LMH6619分别在2个不同的频率下连接到两个ADC的资料。为了用尽ADC的整个动态范围,25VPP的最高输入会施加到ADC的输入。图7表示出在f = 20 KHz时LMH6612和ADC121S625组合的FET绘图。

表3:LMH6612和LMH6619分别连接到ADC121S625和ADC121S70后的效能

图7:差动到差动 ADC驱动器的FET绘图

接地和电路板布局考虑

将输入源接地连接到电源接地是非常重要的。对于上述每一个的ADC驱动器配置,当建立电阻器网络以确保差动输出拥有相同增益时,必须同时考虑讯号源的阻抗。例如,一个音频精确讯号产生器拥有22Ω的源阻抗,而电路板则有一个50Ω的终端,因此设计人员必须调节增益和输入,以便能在运算放大器的输出处获取所需的讯号。

为了获得最佳的高频效能,以下是一些电路板布局的建议:

·将ADC和放大器放置得愈接近愈好

·将供电旁路电容器尽量放近装置(距离少于1英寸)

·采用表面黏着而非穿孔式组件,以及采用接地和电源层

·尽量减少布线的长度

·为冗长布线采用终端式传输线

图8:差动到差动ADC驱动器的电路板布局

LMH6612/LMH6619只消耗仅6.5mA/2.5Ma的电流,相比起市面上大部份的全差动放大器少了超过20mA。采用LMH6611/LMH6612/LMH6618/LMH6619的主要优点是低功率和低成本。当中,LMH6611和LMH6612最适合使用在那些在奈奎斯特(Nyquist)频率20 KHz至2 MHz下运行的应用,而LMH6618和LMH6619则最适合使用在那些在奈奎斯特频率20 KHz至500 MHz下运行的应用。

总括而言,本文涵盖了所有重要的考虑因素,包括外置RL-CL网络的选择以及运算放大器的关键参数:象是THD、设置时间和杂讯,这些都是在把高效能运算放大器连接到ADC时所必须考虑的参数。此外,本文还详细讨论了三种不同的ADC驱动器配置,并且在实验室进行了严谨的测试。最后,本文亦论及接地和电路板布局时需要注意的地方,从而改善系统的效能。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)