硅材料根据晶胞的排列方式不同,分为单晶硅和多晶硅。单晶硅和多晶硅最大的区别是单晶硅的晶胞排是有序的,而多晶硅是无序的。在制造方法方面,多晶硅一般是直接把硅料倒入坩埚中融化,然后再冷却而成。单晶硅是通过拉单晶的方式形成晶棒(直拉法)。在物理性质方面,两种硅的特性相差较大。单晶硅导电能力强,光电转换效率高,单晶硅光电转换效率一般在 17%~25%左右,多晶硅效率在 15%以下。

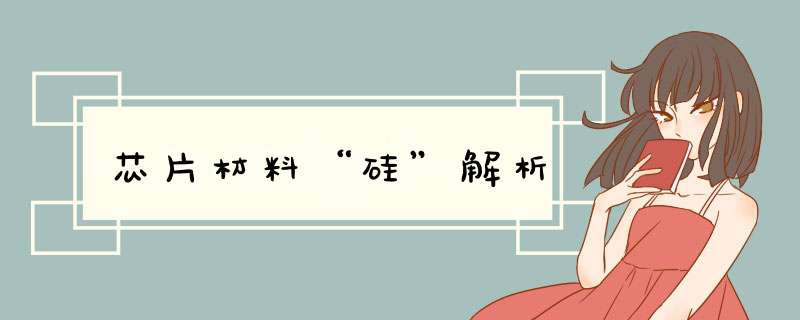

▲半导体硅片和光伏硅片

▲单晶硅晶胞结构

光伏硅片:由于光电效应,且单晶硅优势明显,所以人们使用硅片完成太阳能到电能的转换。在光伏领域使用的一般为圆角方形的单晶硅电池片。价格较便宜的电多晶硅片也有使用,但转换效率较低。

▲单晶硅电池片正反面

▲多晶硅电池片正反面

由于光伏硅片对纯度、曲翘度等参数要求较低,所制造过程相对简单。以单晶硅电池片为例,第一步是切方磨圆,先按照尺寸要求将单晶硅棒切割成方棒,然后将方棒的四角磨圆。第二步是酸洗,主要是为了除去单晶方棒的表面杂质。第三步是切片,先将清洗完毕后的方棒与工板粘贴。然后将工板放在切片机上,按照已经设定好的工艺参数进行切割。最后将单晶硅片清洗干净监测表面光滑度,电阻率等参数。

半导体硅片:半导体硅片比光伏硅片的要求更高。首先,半导体行业使用的硅片全部为单晶硅,目的是为了保证硅片每个位臵的相同电学特性。在形状和尺寸上,光伏用单晶硅片是正方形,主要有边长 125mm,150mm,156mm 的种类。而半导体用单晶硅片是圆型,硅片直径有 150mm(6 寸晶圆),200mm(8 寸晶圆)和 300mm(12 寸晶圆)尺寸。在纯度方面,光伏用单晶硅片的纯度要求硅含量为 4N-6N 之间(99.99%-99.9999%),但是半导体用单晶硅片在 9N(99.9999999%)-11N(99.999999999%)左右,纯度要求最低是光伏单晶硅片的 1000 倍。在外观方面,半导体用硅片在表面的平整度,光滑度和洁净程度要比光伏用硅片的要求高。纯度是光伏用单晶硅片和半导体用单晶硅片的最大不同。

▲半导体硅片制造过程

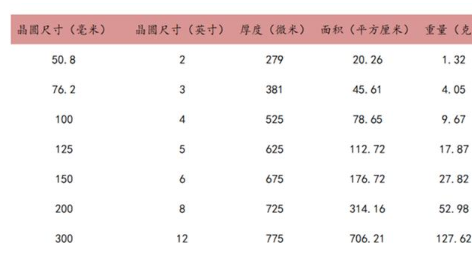

摩尔定律的发展就是硅片的发展。由于半导体用硅片是圆形,所以半导体硅片也叫“硅晶圆”或者“晶圆”。晶圆是芯片制造的“基底”,所有的芯片都是在这个“基底”上制造。在半导体用硅片的发展历程中,主要有尺寸和结构两个方向。

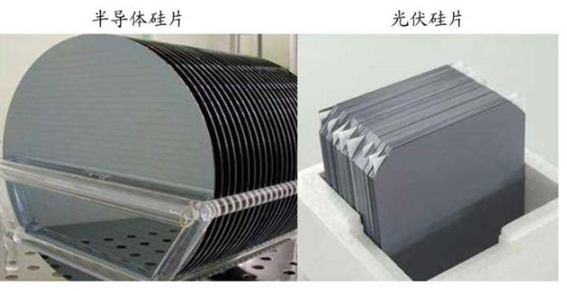

在尺寸上,硅片的发展路径是越来越大:在集成电路发展初期,使用的是 0.75 英寸晶圆。而增加晶圆面积,增加单片晶圆上的芯片个数可以降低成本。1965 年左右,随着摩尔定律的提出,集成电路技术和硅片都迎来快速发展期。硅片经历了4 寸、6 寸、8 寸和 12 寸等节点。自从2001 年英特尔和 IBM联合开发了 12 寸晶圆芯片制造后,现主流硅片就是12寸晶圆,占比约为 70%,但 18寸(450mm)晶圆的已经提上议程。

▲不同尺寸晶圆的参数

▲硅片大小的发展

在结构方面,硅片的发展方向是越来越复杂:集成电路发展初期是只有逻辑芯片一种,但是随着应用场景不断增多,逻辑芯片、功率器件、模拟芯片、数模混合芯片,flash/Dram 存储芯片、射频芯片等等相继出现,使得硅片在结构上出现了不同的形态。现在,主要有以下三种:

PW(Polish Wafer):抛光片。拉单晶后直接切割得到的硅片由于在光滑度或者翘曲度方面不尽完美,所以首先要经过抛光处理。这种方式也是最原始硅片的处理方式。

AW(Anneal Wafer):退火晶圆。随着制程技术的不断发展,晶体管特征尺寸的不断缩小,抛光片的缺点也逐渐 暴露出来,比如硅片表面局部的晶格缺陷,硅片表面含氧量较高等。为了解决这些问题,退火晶圆技术被开发出来。在抛光后,将硅片放在充满惰性气体的炉管中(一般为氩气),进行高温退火。这样既可以修复硅片表面晶格缺陷,同时也可以减少表面含氧量。

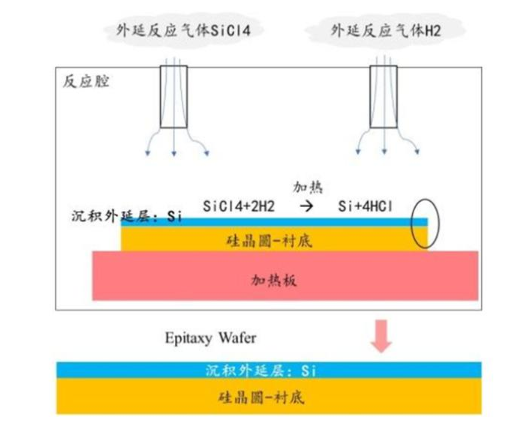

EW(Epitaxy Wafer):外延层硅片。随着集成电路的应用场景不断增加,由硅片厂制造的标准硅片在电学特性上已经不能满足某些产品的要求。同时,通过热退火减少的晶格缺陷也不能满足越来越小的线宽需求。这就衍生出了外延层硅片。通常的外延层就是硅薄膜。是在原始硅片的基础上,利用薄膜沉积技术,生长一层硅薄膜。由于在硅外延中,硅基片是作为籽晶的模式存在,所以生长外延层会复制硅片的晶体结构。由于衬底硅片是单晶,所以外延层也是单晶。但是由于没有被抛光,所以生长完成后的硅片表面的晶格缺陷可以被降到很低。

外延技术指标主要包括外延层厚度及其均匀性、电阻率均匀性、体金属控制、颗粒控制、层错、位错等缺陷控制。现阶段人们通过优化外延的反应温度、外延气体的流速、中心及边缘的温度梯度,实现了很高的外延层硅片质量。因产品不同和技术升 级的需要,通过不断优化外延工艺,现在已经实现了很高的外延硅片质量。

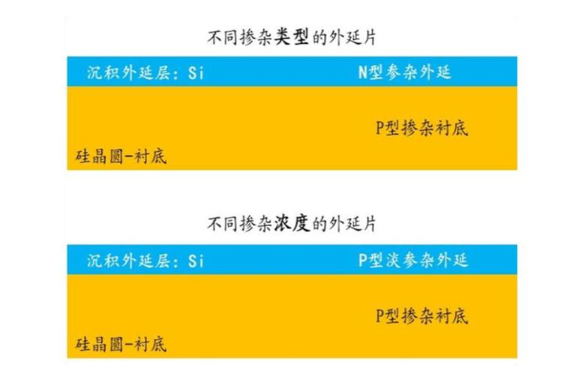

另外,现在技术已经可以生成电阻率掺杂元素、掺杂浓度与原始硅片不同的外延层,这样更容易控制生长出来的硅片的电学特性。比如可以通过在 P 型硅片上生成一层 N 型硅外延层,这样就形成了一个低浓度参杂的 PN 结,为后续芯片制造中起到优化击穿电压,降低闩锁效应等等目的。外延层厚度一般根据使用场景不同而不同,一般逻辑芯片的厚度为 0.5 微米到 5微米左右,功率器件由于需要承受高电压,所以厚度为 50 微米到 100 微米左右。

▲外延硅片生长过程

▲外延片的不同参杂

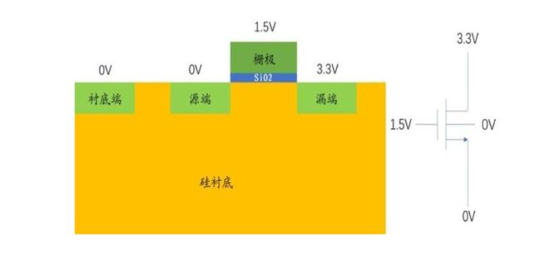

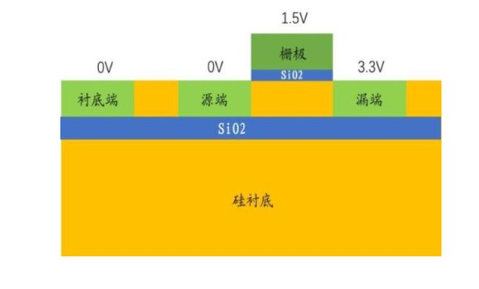

SW(SOI Wafer):SOI 全称是 Silicon-On-Insulator(绝缘体上硅)。由于 SOI 硅片具有寄生电容小、短沟道效应小、继承密度高、速度快、功耗低等优点,特别是在衬底噪声低这个优点使得 SOI 硅片常常用在射频前端芯片中。

▲普通硅片 MOS 结构

▲SOI 硅片 MOS 结构

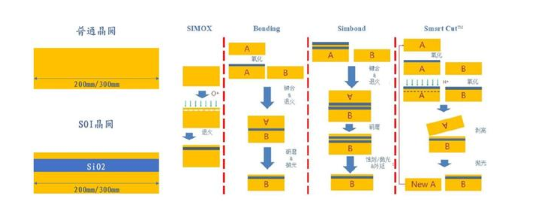

制造 SOI 硅片的方法主要有四种:SIMOX 技术、Bonding 技术、Sim-bond 技术和 Smart-CutTM 技术;SOI 硅片的原理比较简单,核心目标就是在衬底中间加入一层绝缘层(一般以二氧化硅 SiO2 为主)。

▲四种制造 SOI 硅片技术

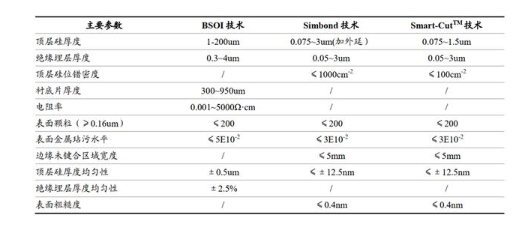

从性能参数上来看,Smart-CutTM 技术是现在 SOI 硅片制造技术中性能最优异的。Simbond 技术性能和 Smart-Cut 技术性能相差不大,但是在顶层硅厚度方面,Smart-Cut 技术生产的 SOI 硅片更薄,而且从生产成本来说,Smart-Cut 技术可以重复利用硅片,对于未来的大批量生产情况,Smart-Cut 技术更有成本优势,所以现在业界公认以 Smart-Cut 技术为未来 SOI 硅片发展方向。

▲SOI 硅片不同制造技术的性能对比

SIMOX 技术:SIMOX 全称 SeparaTIon by Implanted Oxygen(注氧隔离技术)。向晶圆中注入氧原子,然后经过高温退火,使氧原子与周围的硅原子发生反应,生成一层二氧化硅。此项技术的难点是控制氧离子注入的深度与厚度。对于离子注入技术要求较高。

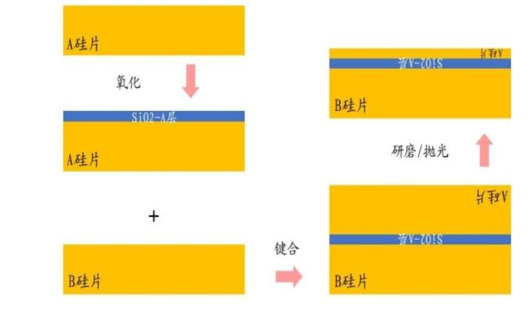

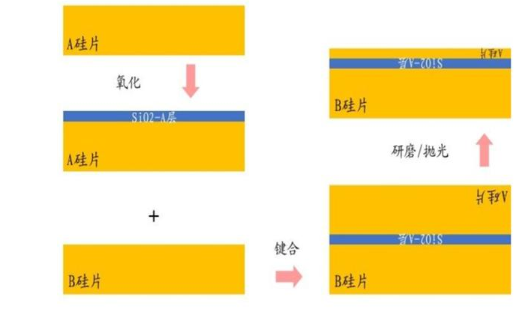

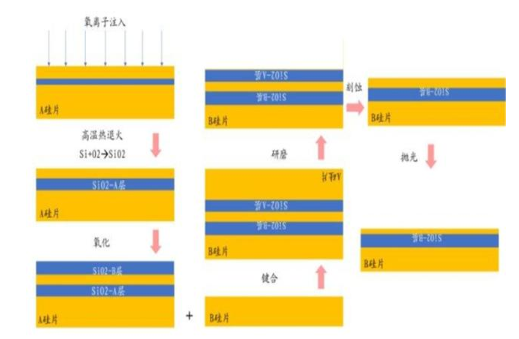

Bonding 技术:Bonding 技术又称键合技术,用 bonding 制造的 SOI 硅片又叫 Bonded SOI,简称 BSOI。Bonding技术需要两片普通硅晶圆,在其中一片上生长一层氧化层(SiO2),然后与另外一片硅源键合,连接处就是氧化层。最后再进行研磨和抛光到想要的填埋层(SiO2)深度。由于键合技术比离子注入技术简单,所以目前 SOI 硅片大都采用 bonding 技术制作。

▲离子注入方式形成绝缘体上硅

▲wafer bonding 方式形成绝缘体上硅

Sim-bond 技术:注氧键合技术。Sim-bond 技术是 SIMOX 与 bond 技术的结合。优点是可以高精度控制埋氧层厚度。第一步是向一片硅晶圆注入氧离子,然后高温热退火形成氧化层,然后在该硅片表面形成一层 SiO2 氧化层。第二步是将该硅片与另外一片晶圆键合。然后进行高温退火形成完好的键合界面。第三步,减薄工艺。利用 CMP 技术减薄,但是与 bond 技术不同的是,sim-bond 有自停止层,当研磨到 SiO2 层时,会自动停止。然后经过腐蚀去掉 SiO2层。最后一步是抛光。

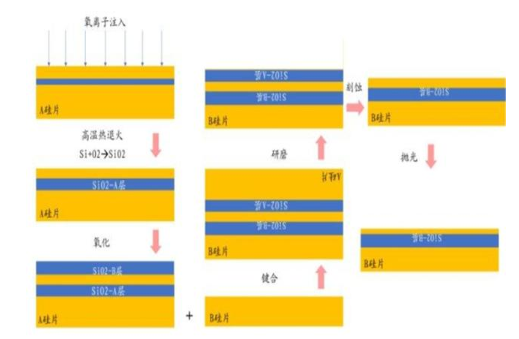

Smart-cut 技术:智能剥离技术。Smart-cut 技术是键合技术的一种延伸。第一步是将一片晶圆氧化,在晶圆表面生成固定厚度的 SiO2。第二步是利用离子注入技术,向晶圆的固定深度注入氢离子。第三步是将另外一片晶圆与氧化晶圆键合。第四步是利用低温热退火技术,氢离子形成气泡,令一部分硅片剥离。然后利用高温热退火技术增加键合强度。第五步是将硅表面平坦化。这项技术是国际公认的 SOI 技术发展方向,埋氧层厚度完全由氢离子注入深度决定,更加准确。而且被剥离出的晶圆可以重复利用,大大降低了成本。

▲sim-bond 方式形成绝缘体上硅

▲Smart-cut 方式形成绝缘体上硅

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)