1996年,家喻户晓的通用串行接口(USB1.0)初次问世,它可以支持低速(LS)模式和全速(FS)模式,分别提供1.5Mbps和12Mbps的速率。2000年,USB2.0面市,其新的高速(HS)模式可提供高达480Mbps的速率,并且依然向下兼容低速模式和全速模式。

目前,USB2.0是最普遍的通用外部数据接口之一,且事实上已成为便携式电脑、上网本和台式机等所有计算机系统的标配接口。此外,诸如便携式摄像机、数码相机、MP3播放器、电子游戏机、DVD蓝光播放器和电视机,以及手机和DSL/路由器等消费电子产品,也广泛采用USB2.0接口。

2008年,30亿个带USB2.0接口的新电子设备进入市场。预计2013年将有超过40亿个具备USB接口的新电子设备上市。随着超高速应用的发展,对具有更高数据率的外部接口的需求与日俱增,例如将外部硬盘驱动器连接至计算机。

在市场上,有些系统可提供比USB2.0高速模式480Mbps高得多的数据率。例如,千兆以太网的速度是其3倍左右,外部串行 ATA(eSATA)则可提供3Gbps的数据率(约6倍)。但所有这些系统均不向下兼容USB2.0接口,因为它们采用的是不同的系统方法。

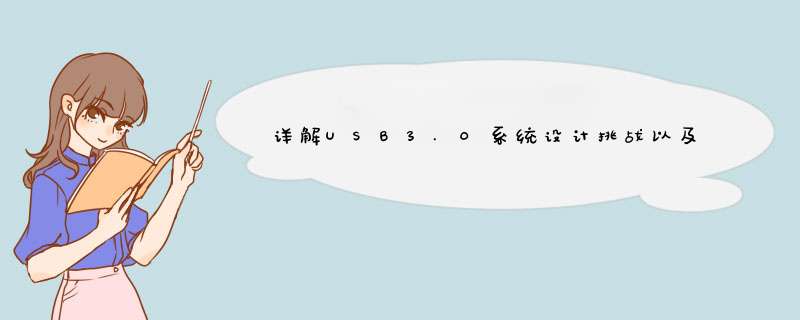

USB3.0系统设计挑战2008年11月,USB3.0规范发布。USB3.0不仅包含USB2.0的全部功能(HS、FS和LS),而且可提供名为超高速 (SuperSpeed)的单独的全新超高速数据链路。超高速链路为下载(从主机到设备,被称为发送方向)和上传(从设备到主机,被称为接收方向)提供了单独的差分数据线路。超高速模式可提供的最高数据率为5Gbps(图1)。

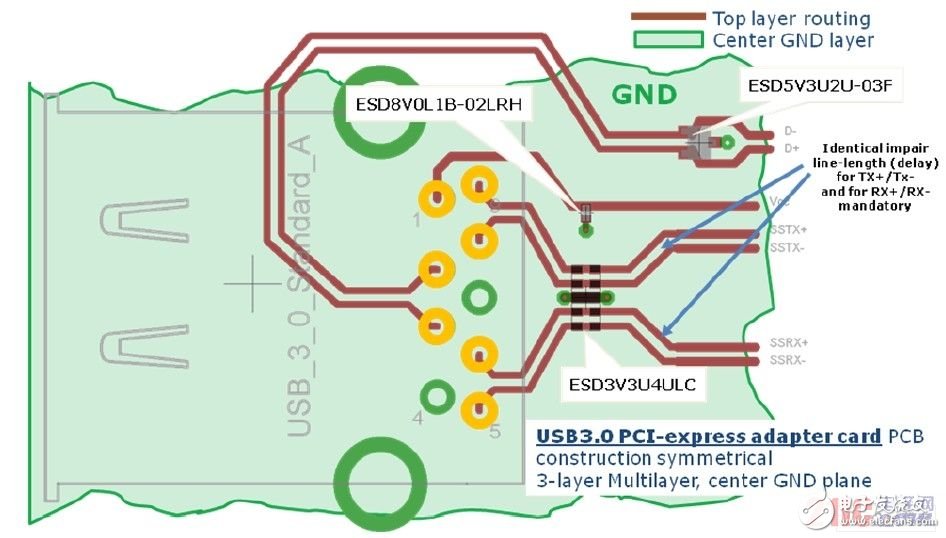

USB3.0物理链路在主机侧和设备侧带有ESD防护

图 1:USB3.0物理链路在主机侧和设备侧带有ESD防护。

为同时支持USB2.0功能和新的超高速模式,电缆必须采用新的结构,以提供三条差分耦合信号线(TX+/Tx-、RX+/Rx-和D+/D-)。此外,USB3.0电缆还必须具备Vcc线和GND线。这种低成本的USB3.0电缆所面临的挑战,是需支持很高的截止频率且不会在相邻的差分耦合线对之间形成干扰(图2a)。

USB3.0电缆结构

图 2a:USB3.0电缆结构。

为支持USB3.0电缆所包含的全部线路,必须强制规定采用一种新的连接器形状。新的USB3.0连接器的基本要求,是必须向下兼容USB2.0连接器。从ESD的角度看,这导致标准A连接器的超高速线路很容易发生ESD冲击(在主机侧和设备侧)。一种强有力的对策是在USB3.0链路中实现有效的ESD防护机制。

USB3.0电缆结构图 2a:USB3.0电缆结构。

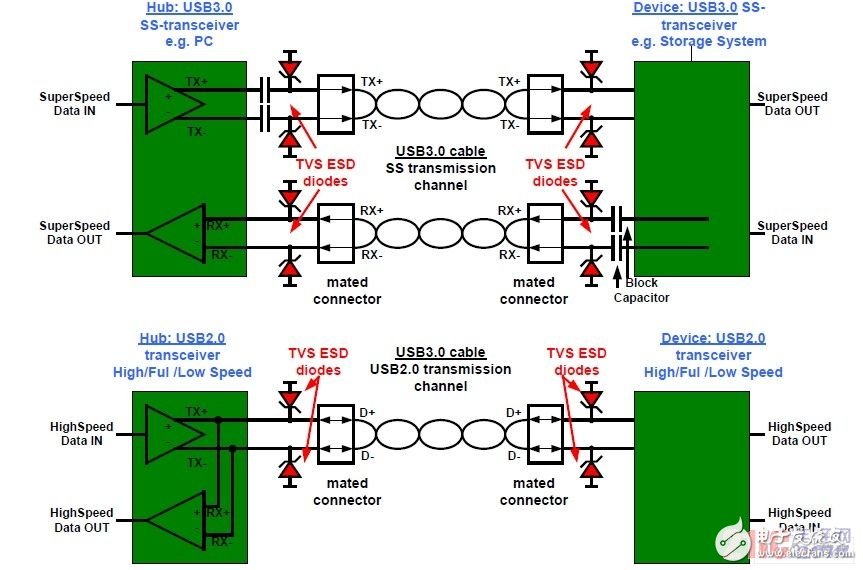

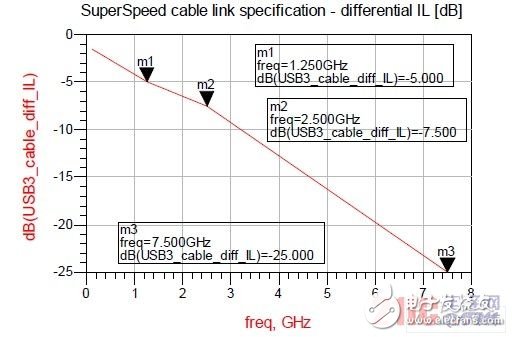

超高速数据传输系统面临的一个最严峻的问题,是确保在接收端实现一定程度的信号完整性。很高的信号完整性有助于实现很低的误码率(例如,对于 USB3.0超高速模式,典型误码率为1E-12)。眼图描述了信号完整性的特性。在拥有无限带宽的完美系统中,眼图完全张开。在实际的系统中,发送和接收阻抗(90欧姆差分阻抗)以及发送侧和接收侧的所有寄生电容,限制了信号的上升时间/下降时间。这些寄生电容存在于USB3.0收发器内部和/或PCB 外部。不匹配的PCB线路、USB3.0连接器或其它并联电容器等,均会造成外部寄生电容。因此,这些额外的并联电容器必须尽可能小。还必须考虑到USB3.0电缆的低通频率响应(图2b)。为抵消高频内容的衰减,可在发送侧和接收侧利用专用均衡器改变信号。这些措施均有助于加快信号上升和下降边的速度,从而得到张得更开的眼图(即更高的信号完整性)(见图3a和图3b)。

为实现适当的信号完整性性能,TVS二极管的电容必须很低,但TVS二极管也必须提供较高的ESD包含水平。

图4a、b为整个USB3.0链路的眼图模拟图(误码率为1E-6)。在图4a中,所用的接收信号是在未经接收端均衡器处理之前。在图4b中,所用的接收信号是经接收端均衡器处理之后。红色的内轮廓线所示为用外推法得到的误码率为1E-12时的眼图张开程度。红紫色轮廓线为USB3.0技术规范中规定的超高速一致性测试的有效值。比较这两个眼图,在接收端使用均衡器的效果显而易见。

图4a:未经接收端均衡器处理之前的信号眼图。 图4b:经接收端均衡器处理之后的信号眼图。

图4a:未经接收端均衡器处理之前的信号眼图。 图4b:经接收端均衡器处理之后的信号眼图。

超高速链路和USB2.0传输链路采用了差分耦合90欧姆线路。链路内部的阻抗不匹配造成的信号反射会降低信号完整性。为避免出现这种情况,包括USB3.0电缆在内的整个布局设计,应当实现90欧姆差分阻抗匹配。

为尽量减少斜率下降,并且提供相同的延迟时间,所有差分耦合线路均必须为相同的长度。对USB3.0电缆而言,这一点尤为重要。斜率下降的多会降低信号完整性,从而导致所谓的“差模共模信号转换”。所产生的共模信号会影响EMI测试的顺利进行。阻抗匹配的适当布局设计,能避免这些问题。

USB3.0超高速链路和USB2.0链路的布局布线考虑在整个USB3.0链路的布局布线设计中,应考虑下列因素:(1)所有PCB线路和互连电缆均采用完全阻抗匹配的90欧姆差分设计。(2)必须最大限度地减少非差分耦合线路。(2)非差分耦合线路会严重影响眼图的内眼张开程度。(3)90欧姆差分耦合PCB线路的线路宽度和线路间隔不应太窄,以避免造成额外的损耗,同时便于生产。从生产的角度而言,差分线路的理想线路宽度为0.3毫米,线路间隔为0.2毫米,这会形成200微米的电介质高度(假设FR4,且er=4)。(4)差分耦合链路的正电和负电线路(包括USB3.0电缆)之间的延迟(线路长度)完全相同(最大限度地减少斜率下降)。对于保持很高的信号完整性和避免生成共模信号,这一点很重要。

图5为具备ESD防护电路的USB3.0标准A连接器横截面的布局布线设计示例。

具备ESD防护电路的标准A连接器USB3.0布局布线设计建议

图 5:具备ESD防护电路的标准A连接器USB3.0布局布线设计建议。

USB3.0的新型ESD防护策略持续不断地减小芯片的各个组件的尺寸是降低生产成本、提高工作频率的根本,但与此同时,这种微型化也产生了新的问题(如容易发生ESD击穿)。因此,对提供可靠的ESD防护机制的要求与日俱增。

USB3.0可提供最高5Gbps的数据率,因此基本频率高达2.5GHz。为实现很高的信号完整性,数据信号的上升时间和下降时间必须非常短。对第3谐波或第5谐波的处理,不应发生明显衰减。这些只能通过利用寄生效应最小、半导体开关速度最快的尖端半导体制程才能实现。这种微型化半导体结构的缺点,是对ESD冲击造成的过压的耐受能力降低。采用内置ESD防护装置,会引起寄生效应(寄生电容),并且需要占用很大的片上空间。

一种十分经济高效的方法,是同时采用内置ESD防护机制(集成到USB3.0收发器中),以及专为提供外部ESD防护而定制的性能增强(即高电流)应用电路(由器件/电路设计者在电路板上实现)。内置ESD防护机制旨在提供器件级保护,例如,严格遵守HBM JEDEC JESD 22-A115要求。内置ESD防护对在开发、生产和电路板装配过程中安全地拿放器件很重要。专为该应用定制的外部TVS二极管则按照 IEC61000-4-2标准,实现了更加严格的系统级保护。

为提供适当的USB3.0系统级ESD防护,ESD防护器件(TVS二极管)必须满足不同的要求。可参照IEC61000-4-2标准,根据残留箝位电压和TVS二极管对ESD冲击的响应,判断TVS二极管的ESD防护性能。

TVS二极管的ESD防护性能会受TVS二极管的一些特性影响,比如最低R_on(动态电阻R_dynamic)和专为该应用定制的最低V_breakdown。

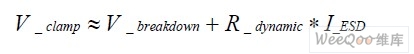

根据经验,可以计算出箝位电压(V_clamp):

为确保应用的安全,压敏电压必须与所保护的线路上的最高电源电压和最高信号电平相一致。动态电阻(R_dyn)应当尽可能小。结合最优压敏电压和最低动态电阻,可最大限度地减小IC上的残留ESD应力。

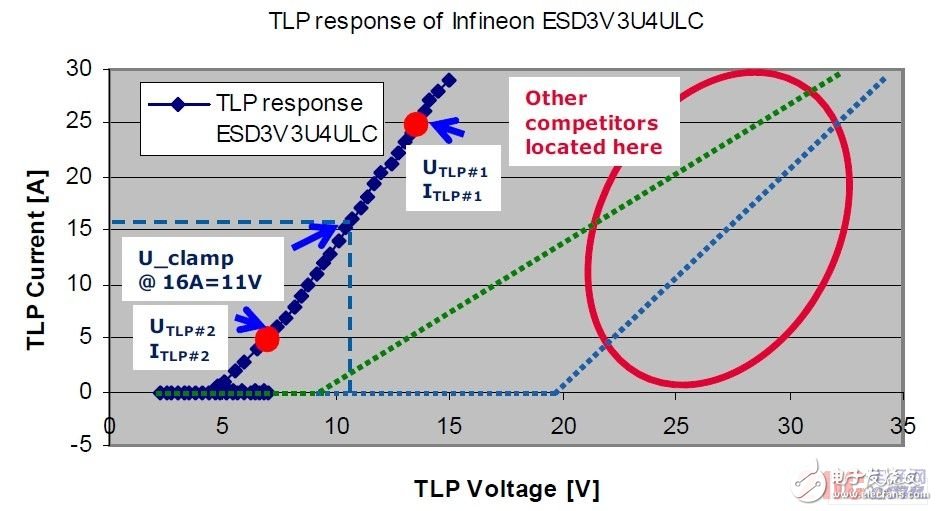

可根据传输线路脉冲(TLP)测定值,推导出动态电阻(图5)。

专为USB3.0超高速模式提供ESD防护而定制的英飞凌ESD3V3U4UL TVS二极管的TLP测定结果

图6:专为USB3.0超高速模式提供ESD防护而定制的英飞凌ESD3V3U4UL TVS二极管的TLP测定结果。

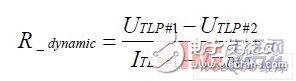

根据TLP测定图,可计算出动态电阻(图6):

为对USB3.0超高速链路提供静电防护,英飞凌专为该应用定制了一只动态电阻仅为0.3欧姆左右、最高反向工作电压为3.3V(压敏电压最低4V)的TVS二极管(ESD3V3U4ULC)。在测试中,16A的ESD冲击的箝位电压为11V,这在当今市场上的同类产品中堪称佼佼者。

备注:按照IEC61000-4-2标准,所用16A TLP测试脉冲非常适合8KV接触ESD冲击,在30ns点上提供了16A的ESD电流。

为保护另外的USB2.0链路,TVS二极管必须提供稍高一些的反向工作电压/压敏电压。为支持全速和低速模式,必须提供更高的压敏电压,从而形成最高+5V左右的信号振幅。英飞凌ESD5V3U1U和ESD5V3U2U系列可提供最低5.3V的反向工作电压(压敏电压最低6V),二极管电容典型值为0.4pF。

带ESD防护的USB3.0超高速链路的信号完整性分别在带ESD防护和未带ESD防护的情况下,对图1所示的整个USB3.0超高速链路执行了信号完整性模拟。

整个收发部分具备90欧姆差分阻抗,考虑了发送侧和接收侧的寄生效应。测得数据表明了USB3.0电缆的状态。规定最长USB3.0电缆长度为3米。

为对USB3.0超高速链路提供ESD防护,在主机侧和设备侧均配置了英飞凌ESD3V3U4ULC。ESD3V3U4ULC具备卓越的ESD防护性能,并且二极管电容(二极管对地)极低,典型值为0.5pF。

在模拟中考虑了USB3.0超高速链路的基本布局布线设计规则(见图5)

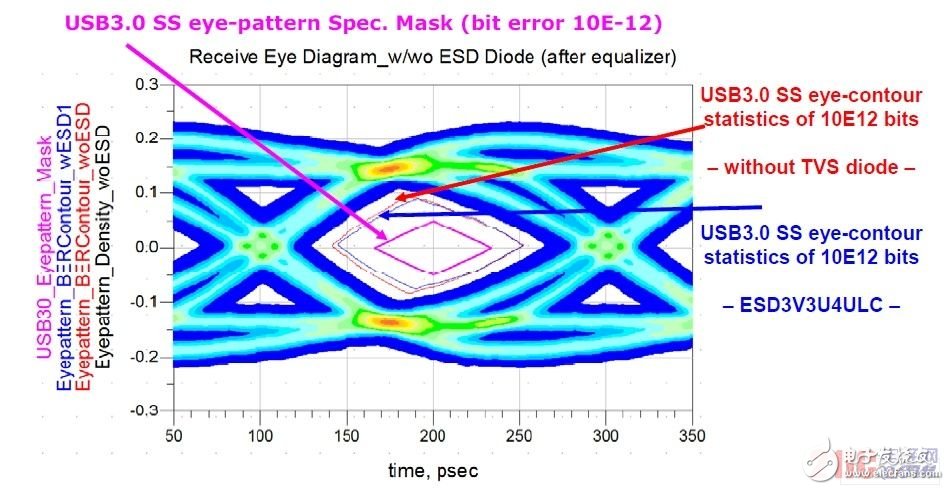

在对整条USB3.0超高速链路执行的信号完整性模拟中,按照USB3.0一致性测试标准参数,实现了发送侧信号去加重和接收端均衡器,并分析了经接收端均衡器处理之后的超高速信号的眼图。模拟所用误码率为1E6。根据模拟结果,推导出误码率为1E12时的眼图张开程度(红色和蓝色轮廓线)。

分别在未带TVS二极管(红色轮廓线)和带有TVS二极管(ESD3V3U4ULC,蓝色轮廓线)的情况下,计算出眼图的张开程度(图7)。

在主机侧和设备侧带和未带ESD3V3U4ULC时的眼图图7:在主机侧和设备侧带和未带ESD3V3U4ULC时的眼图。

在主机侧和设备侧带有超低电容TVS二极管ESD3V3U4ULC,眼图张开程度(轮廓线)会受到一定影响。虽然眼图张开程度会略微减小,但相比于USB3.0技术规范中规定的基准模式(红紫色轮廓线),仍大出许多。

本文小结必须精心设计USB3.0链路,以实现最优系统级ESD防护性能,并且强制要求实现毫厘不差的信号完整性。为同时满足这两个要求,ESD防护器件必须具有卓越的ESD防护性能和很低的器件电容。采用“阵列”配置的英飞凌ESD3V3U4ULC,结合清楚明了的布局布线设计和高质量链路 (USB3.0电缆),能够实现上述要求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)