差分驱动器基础知识

目前许多高性能ADC设计均采用差分输入。全差分ADC设计具有共模抑制性能出色、二阶失真产物较少、直流调整算法简单的优点。尽管可以单端驱动,但全差分驱动器通常可以优化整体性能。

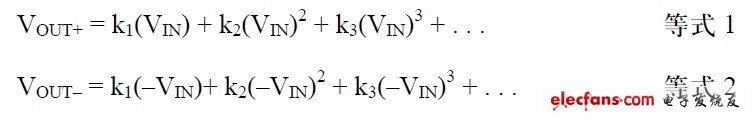

差分设计固有的低二阶失真产物如下所示。失真产物可以通过将电路传递函数表达为幂级数来建立模型。

进行输出一般扩展并假设放大器匹配,我们得到:

采用差分输出:

其中k1、k2和k3为常数。

二次项引起二阶谐波失真,三次项引起三阶谐波失真,如此等等。在一个全差分放大器中,奇数阶项保留极性,而偶数阶项则始终为正。当采取差分时,偶数阶项如等式3所示消除。三阶项不受影响。

差分输入ADC的一种最常用驱动方法是使用变压器。不过,因为频率响应必须延伸至直流,许多应用无法使用变压器来驱动。这类情况就需要使用差分驱动器。在ADC前面需要明显信号增益的情况下,差分放大器提供一种不错的解决方案。尽管提供"无噪声"电压增益,但匝数比大于2的变压器一般为带宽和失真问题所困扰,在中频时尤为明显。

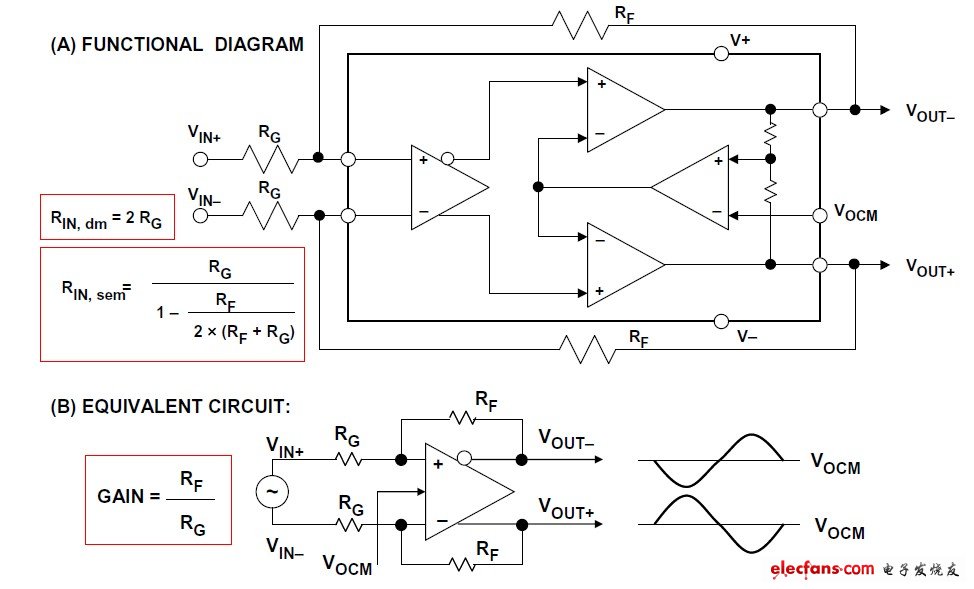

图1所示为驱动ADC而优化的AD813x和ADA493x系列全差分放大器框图。图1A显示内部电路细节,而图1B显示等效电路。增益由外部电阻RF和RG设定,共模电压由VOCM引脚上的电压设定。内部共模反馈强制VOUT+和VOUT–输出保持平衡,即在两个输出端的信号根据等式幅值始终相等,但相位相差180°。

图1:AD813x、AD493x差分ADC驱动器功能框图及等效电路。

AD813x和ADA493x用两个反馈环路,来分开控制差分输出电压和共模输出电压。外部电阻设定的差分反馈只控制差分输出电压。共模反馈控制共模输出电压。这种架构方便在电平转换应用中任意设定输出共模电平。内部共模反馈强制其等于VOCM输入上施加的电压,而不影响差分输出电压。其结果是近乎完美的平衡差分输出,在宽广的频率范围内其幅度完全相同,相位相差180°。该电路可配合差分或单端输入使用,且电压增益等于RF与RG之比。

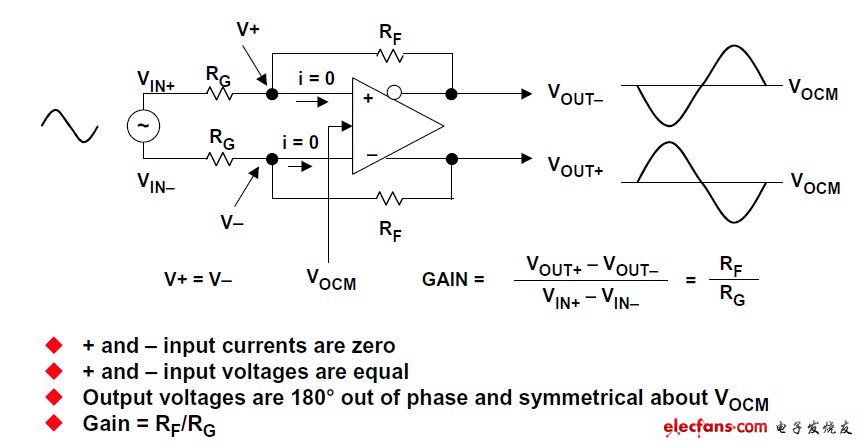

该电路可使用图2中所归纳的假设和程序来分析。如同运算放大器电路直流分析的情况,我们可以先假设流入反相和同相输入的电流为零(即输入阻抗相对反馈电阻值较高)。第二个假设为反馈强制同相和反相输入电压相等。第三个假设为输出电压相位相差180°并在VOCM两侧对称。

图2:差分放大器电平分析

即使外部反馈网络(RF/RG)不匹配,内部共模反馈环路仍将强制输出保持平衡。每个输出端的信号幅度保持相等,相位相差180°。输入到输出的差模增益变化与反馈的不匹配成比例,但输出平衡不受影响。外部电阻的比例匹配误差会导致电路抑制输入共模信号的能力降低,非常类似于使用常规运算放大器制成的四电阻差动放大器。

而且,如果输入和输出共模电压的直流电平不同,匹配误差会导致一个细小的差模输出失调电压。对于G = 1,具有一个地基准输入信号且针对2.5 V设定输出共模电平的情况,如果使用1%容差电阻,则可产生高达25 mV的输出失调(1%共模电平差)。由于2.5 V电平转换,1%容差的电阻将导致一个约40 dB的输入CMR(最差情况)、25 mV的差模输出失调(最差情况),不会对输出平衡误差造成明显恶化。

如图2所示电路的有效输入阻抗(在V IN+和V IN–端)取决于放大器是由单端信号源驱动,还是由差分信号源驱动。对于平衡差分输入信号,两个输入端(V IN+和V IN– )之间的输入阻抗(R IN,dm )为:

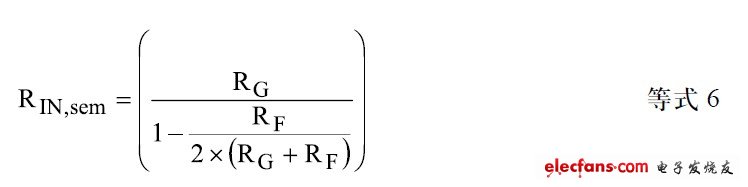

若为单端输入信号(例如,若V IN–接地,输入信号接入V IN+ ),输入阻抗则为:

该电路的单端输入阻抗高于作为反相放大器连接的常规运算放大器,因为一小部分差分输出电压在输入端表现为共模信号,从而部分增加了输入电阻RG两端的电压。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)