1引 言

AD7714是适用于低频测量应用的完整模拟前端。器件直接从传感器接受低电平信号并输出串行数字。它使用和 -差(Σ-Δ)转换技术以实现高达24位的无误码性能。输入信号加至专有的基于模拟调制器、具有可编程增益的前端。调制器的输出由片内数字滤波器处理 。通过片内控制寄存器可对此数字滤波器的第一个凹口编程,允许调整滤波器的截止频率和稳定时间。AD7714具有3个差分模拟输入(它也可以配置为5个准差分模拟输入)以及差分基准输入,可以对多达5个通道的系统实现信号调理和转换。

2引脚定义及功能

DIP封装的AD7714如图1。各引脚定义如下:

图1 AD7714的封装及其引脚

引脚1 SCLK:串行时钟。逻辑输入端,外部串行时钟加 至此端以存取来自AD7714的串行数据。

引脚2 MCLKIN:器件的主时钟信号。可以用晶振或外部 时钟提供。器件规定的时钟输入频率为1MHz和2.4576MHz。

引脚3 MCLKOUT:配合MCLKIN使用,当器件的主时钟是晶振时,晶振跨接在MCLKIN 和MCLKOUT引脚之间。

引脚4 POL:时钟极性,逻辑输入端。它决定了在与微控制器之间传送数据时,串行时钟应闲置为高电平还是低电平。POL为低,闲置为低,POL为高,闲置为高。

引脚5 SYNC:逻辑输入端 ,当使用多个AD7714时,它用于数字滤波器和模拟调制器的同步。一般单个使用时都接高电平。

引脚6 RESET:逻辑输入端,低电平有效输入,它把器件的控制逻辑、接口逻辑、数字滤波器以及模拟调制复位到上电状态。

引脚7(8) AIN1(AIN2):可编程模拟输入通道1(2)。与AIN6一起用时作为准差分输入端;与AIN2(AIN1)一起用时作为差分输入对的正(负)输入端。

引脚9(10) AIN3(AIN4):可编程模拟输入通道3(4)。与AIN6一起用时作为准差分输入端;与AIN4(AIN3)一起用时作为差分输入对的正(负)输入端。

引脚16 AIN5:可编程模拟输入通道5。与AIN6一起用时作为差分输入对的正输入端。

引脚17 AIN6:模拟输入通道6。它是准差分模式下AIN1到AIN4的基准点;与AIN5一起用时作为差分输入对的负输入端。

引脚11 STANDBY:把此引脚置为低电平将关断模拟和数字电路,电流消耗减至5 mA(典型值)。

引脚13 BUFFER:逻辑输入端。低电平时AVDD线中流过的电流减至270 mA;高电平时使输入端有较高的源阻抗。

引脚14 REFIN(-):差分基准输入的负输入端,只要REFIN(+)大于REFIN(-)的条件下,则REFIN(-)可位于AVDD和AGND之间的任何值。

引脚15 REFIN(+):差分基准输入的正输入端,在REFIN(+)必须大于REFIN(-)的条件下,基准输入是差分的。REFIN(+)可位于AV DD和AGND之间的任何值。

引脚19 CS:片选逻辑输入端,低电平有效。

引脚20 DRDY:逻辑输出端。它是AD7714的数据寄存器有新的数字可供使用的标志。

引脚21 DOUT:AD7714的串行数据输出端。通过它输出片内寄存器信息以及模拟转换后的数据。

引脚22 DIN:AD7714的串行数据输入端。通过它将串行数据输入片内寄存器(数据寄存器除外)。

引脚12 AVDD:为模拟正电源电压。

引脚18 AGND:模拟电路的地基准点。

引脚23 DVDD:数字正电源电压。

引脚24 DGND:数字电路的地基准点。

3AD7714的片内寄存器剖析

AD7714包含8个片内寄存器,它们可以通过器件的串行口访问。

3.1通信寄存器

它控制通道的选择。在上电和复位之后,器 件等待对其通信寄存器的写 *** 作。写至寄存器的数据决定对器件的下一次 *** 作是读还是写,并决 定对哪一个寄存器发生读或写 *** 作。随后对所选择的寄存器的读或写(一般数据寄存器不进行写 *** 作 ) *** 作。一旦完成后续的对所选择寄存器的读和写 *** 作,接口便返回到等待对通信寄存器写 *** 作的状态。因此,所有与器件的通信必须从对通信寄存器的写 *** 作开始。另外,通过读通信寄 存器还可以获取DRDY的状态。该寄存器的格式为表1。

![]()

表中0/DRDY对于写 *** 作,必须把0写入该 位,否则写将无效。对于读 *** 作,该位将提供器件的DRDY标志,它与芯片的DRDY输出引脚相同。

RS2~RS0为寄存器选择位,对该寄存器写 时,由这3位决定对8个片内寄存器中哪一个发生下一次的读或写 *** 作。RS2为最高位,RS0为最 低位,RS2RS1RS0从000至111分别对应通信寄存器,模式寄存器,滤波器高寄存器,滤波器低 寄存器,测试寄存器,数据寄存器,零刻度校准寄存器,满刻度校准寄存器。

CH2~CH0为通道选择。这3个位选择用作转 换或用作访问校准系数的通道,如表2。

3.2模式寄存器

它是8位寄存器,可从中读出数据或把数据写 入其中,寄存器格式如表3。

表3中MD2~MD0为AD7714的工作模式选择位。MD2为最高位,MD0为最低位,MD2、MD1、MD0从000至111分别对应正常模 式、自校准、零刻度系统校准、满刻度系统校准、系统失调校准、背景校准、零刻度自校准、 满刻度自校准;

G2~G0为增益设置。G2、G1、G0从000至111分别对应的增益为1、2、4、8、16、32、 64、128。

BO为烧断电流。上电或复位状态为0。此位 为1时烧断电流连接至所选的模拟输入对,一个连接到AIN(+)输入端,一个连接到AIN( -)输入端。

FSYNC为滤波器同步。此位为高电平时,数 字滤波器的结点、滤波器控制逻辑、校准控制逻辑以及模拟调制器均保持在其复位状态。此位为 低电平时,调制器和滤波器开始处理数据。

3.3滤波器寄存器

由滤波器高寄存器和滤波器低寄存器两个8位 的寄存器构成(格式分别为表4,表5),它们都可读写。

表4中B/U为双极性/单极性工作模式。此位 为0选择双极性工作(上电或复位的缺省状态),此位为1选择单极性工作。

WL为字长度。此位为零则当从数据寄存器读 出时选择十六位字长,此位为1则选择24位字长。

BST为此位为0将减少模拟前端所取电流。为 了减少AVDD吸取的电流,当器件在fCLKIN =1MHz或2.4576MHz、增益为1至4的情况下工作时,此位应当为0;当器件工作于f CLKIN=2.4576MHz、增益为8至128情况下时,此位必须为1,以确保器 件正常工作。

CLKDIS 为主时钟禁止位。此位为1将禁止主时钟出现在MCLKOUT引脚。这样就可以断开 MCLKOUT与系统中其他器件间的时钟信号,以节省功率。

FS11~FS0为滤波器选择。AD7714片内提供 [sin(x)/ x ]3滤波器响应。写入滤波寄存器的这12位数据决定滤波器截止频率、滤波器第一个 凹口的位置以及器件的数据输出速率。与增益一起还决定器件的输出噪声和有效分辨率。滤波器 第1个凹口发生的频率f=fCLKIN/128/ Num。其中Num是位FS0至FS11的十进制等效值,其范围为19~4000 [2]。

3.4测试寄存器

测试器件时使用。上电或复位时缺省为全0。 除测试外一般不用改变该寄存器的内容,否则器件将不能正常工作。

3.5数据寄存器

它是一个只读寄存器,包含器件最近的转换 结果。是否有新的的转换结果由DRDY引脚是否变为低电平决定。通过写滤波器高寄存器的WL 位,寄存器可编程为16位或24位宽度。

3.6零(满)刻度校准寄存器

AD7714包括3个零(满)刻度校准寄存器, 3个寄存器互相完全独立,所以在全差分模式下,每一个输入通道都有一个零(满)刻度寄存器, 这些寄存器的每一个均为24位读/写寄存器,当写这些寄存器时,必须写入24位,否则将没有数据 被送至寄存器。它与相应的满(零)刻度寄存器一起使用以组成寄存器对,分别与各输入通道相联系。

4 AD7714的校准分析

AD7714提供许多校准选项,它们可通过模式 寄存器的MD2、MD1、MD0位来编程。校准周期可以在任何时刻通过写模式寄存器的这些位来开 始。当环境工作温度或电源电压有变化时,应该在器件上启动校准程序。如果在所选的增益、滤 波器凹口或双极性/单极性输入范围方面有变化,也应当启动校准。

4.1自校准

通过把0,0,1写入模式寄存器的MD2、MD1、MD0位,就可以开始器件的自校准。它自动完成零刻度自校准和满刻度自校准两种校准 *** 作。器件也可以分别进行零刻度自校准和满刻度自校准。但进行满刻度校准前必须保证器件已包 含有效的零刻度系数。分别进行校准的意义在于:在完全的自校准时序完成后,可由它本身实 现另外的失调或增益校准,从而调整器件的零点或增益。例如校准参数中的一个(或是失调或是 增益),将不会影响另一个参数。

4.2系统校准

该校准能补偿增益和失调误差以及它自己的内 部误差,也可用于消除模拟输入端源阻抗的任何误差。完成系统校准必须分为两步。即零刻度系 统校准和满刻度系统校准。将零(满)刻度点加至模拟输入端,而后通过把0,1,0(0,1, 1)写入模式寄存器的MD2、MD1、MD0来开始零(满)刻度系统校准。注意,零刻度系统 校准必须先于满刻度系统校准。

4.3背景校准

该校准模式把其校准步骤与正常转换时序相交错,即它提供连续的零刻度自校准。背景校准不提供任何满刻度校准,因此在进行该校准前应当 完成自校准。器件在该校准模式下消除了失调漂移。应当注意,器件在此模式下不应使用SYNC 输入端或FSYNC位。

5 AD7714的工作时序及接口范例

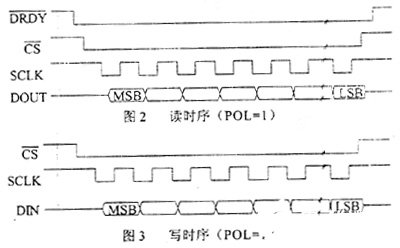

AD7714和AT89C52的接口可以通过两种方式 实现,一种是用AT89C52的RXD(P3.0)与AD7714的DATAIN和DATAOUT进行数据传送, 并利用AT89C52的TXD自带的时钟信号提供给AD7714的SCLK;一种是用AT89C52的某一端 口位(如P1.0)与AD7714的DATAIN和DATAOUT进行数据传送,对另一端口位(如 P1.1)编程产生时钟信号以提供给AD7714的SCLK。图中给出了第一种连接方式,并通过监视 通信寄存器的DRDY位以确定数据寄存器何时有新数据,当然也可以用AT89C52的一个端口位与 AD7714的DRDY引脚相连,以轮询的方式来确定,另外还可以以中断方式来实现。AD7714的 读/写时序图见图2和图3。

与AT89C52的典型接口电路与设计程序的流 程如图4和图5。

图4 AD7714与89C52的接口电路

图5 AD7714程序设计的主要流程图

6 结束语

AD7714以其灵活多样的 *** 作方式和简单的接 口方法深受用户的喜爱,但也必须注意以下几点:

(1)频率的设置与器件转换的有效数据密切相 关,要实现24位无误码,必须保证滤波器的第一个凹口频率小于60Hz。

(2)AD7714的输出噪声、分辨率、增益和第 一个凹口频率是紧密相关的;

(3)AD7714数据输出(写入)的位次序与 AT89C52数据读入(输出)的位次序刚好相反,因此程序中必须安排位颠倒程序。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)