本文研究设计了一种基于高速隔离芯片的高速串行隔离型ADC。该数字隔离型ADC频带宽,延时小,稳定性高并且电路结构简单。利用FPGA作为控制器,很好地实现了模数转换和隔离传输。

2.隔离模块基本工作原理

2.1 工程背景介绍

2.2 高速数字隔离型ADC实现原理

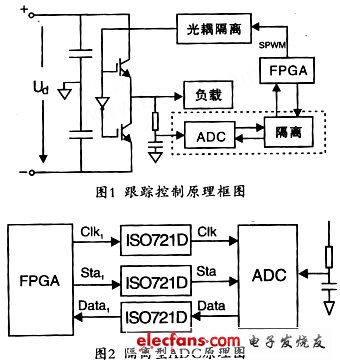

本论文主要研究高速隔离型ADC的实现方案,即图(1)中虚线框内的部分。此部分原理示意图如图(2)所示。图中由FPGA产生两路输出信号分别为Clk1和Sta1。Clk1经过隔离芯片输出信号Clk作为串行ADCMax1072的时钟信号其频率为24MHz。Sta1经过隔离芯片输出信号Sta作为ADC的启动控制信号其频率为1.5MHz。ADC的转换结果为Data信号,经隔离芯片输出Data1信号送回FPGA。

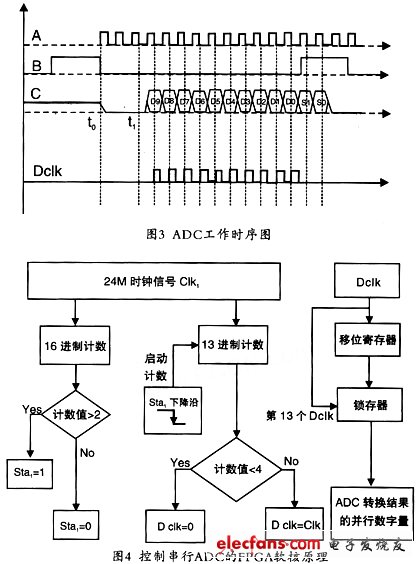

各信号相位关系如图(3)所示。其中,信号A,B,C,Dclk依次为Clk,Sta,Data和FPGA内部移位寄存器的时钟信号,实现将每一位串行数据进行存储。信号B的下降沿启动ADC进行转换,t0~t1时间段内为ADC转换时间,第四个Clk上升沿输出数字量的最高位,经4nS后稳定。依次在每个时钟信号Clk的上升沿产生数字量的下一位,在每个Dclk的上升沿将串行数据锁存在移位寄存器中。在LSB之后还有两位无效位分别为S1和S0。启动信号延时3个Clk,再进行下一次启动。

图(4)为利用FPGA实现的控制隔离型ADC的软核原理描述图。FPGA产生一路频率为24MHz的Clk,信号经过隔离芯片即为图(3)中的信号A,此信号直接输出作为Max1072的时钟信号。Clk1同时也作为启动信号的时钟信号。利用一个16进制计数器对Clk1进行计数产生信号Sta1经过隔离芯片即为图(3)中的信号B。Sta1高电平维持3个Clk1低电平维持13个Clk1。所以Sta1的工作频率为1.5MHz,占空比为12.5%。由Sta1信号的下降沿启动另外一个13进制计数器计数,产生信号经隔离芯片即为如图(3)中所示的信号Dclk。此信号作为移位寄存器的时钟信号,将10位串行数据依次移入寄存器。最后一个时钟信号启动锁存器将串行数据转换成为并行数据锁存在输出端供FPAG内部进行跟踪控制算法使用。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)