赛灵思 INT8 优化为深度学习推断提供了性能最佳、能效最高的计算技术。赛灵思的集成式 DSP 架构与其他 FPGA DSP 架构相比,在INT8 深度学习运算上能实现 1.75 倍的解决方案级性能。

概要本白皮书旨在探索实现在赛灵思 DSP48E2 Slice 上的 INT8 深度学习运算,以及与其他 FPGA 的对比情况。在相同资源数量情况下,赛灵思的 DSP 架构凭借 INT8在 INT8 深度学习每秒运算次数 (OPS) 上相比其它 FPGA,能实现 1.75 倍的峰值解决方案级性能。由于深度学习推断可以在不牺牲准确性的情况下使用较低位精度,因此需要高效的 INT8 实现方案。

赛灵思的 DSP 架构和库专门针对 INT8 深度学习推断进行了优化。本白皮书介绍如何使用赛灵思 UltraScale 和 UltraScale+ FPGA 中的DSP48E2,在共享相同内核权重的同时处理两个并行的 INT8 乘法累加 (MACC) 运算。本白皮书还阐述了要运用赛灵思这一独特技术,为何输入的最小位宽为 24 位。本白皮书还以 INT8优化技术为例,展示了该技术与神经网络基本运算的相关性。

用于深度学习的 INT8深度神经网络(DNN)已掀起机器学习领域的变革, 同时运用新的达到人类水平的 AI 功能重新定义众多现有的应用。

随着更精确的深度学习模型被开发出来,它们的复杂性也带来了高计算强度和高内存带宽方面的难题。能效正在推动着深度学习推断新模式开发方面的创新,这些模式需要的计算强度和内存带宽较低,但绝不能以牺牲准确性和吞吐量为代价。降低这一开销将最终提升能效,降低所需的总功耗。

除了节省计算过程中的功耗,较低位宽的计算还能降低内存带宽所需的功耗,因为在内存事务数量不变的情况下传输的位数减少了。

研究显示要保持同样的准确性,深度学习推断中无需浮点计算[ 参考资料 1][ 参考资料 2][ 参考资料 3],而且图像分类等许多应用只需要 INT8 或更低定点计算精度来保持可接受的推断准确性[ 参考资料 2][ 参考资料 3]。表 1 列出了精调网络以及卷积层和完全相连层的动态定点参数及输出。括号内的数字代表未精调的准确性。

表 1 :带定点精度的 CNN 模型

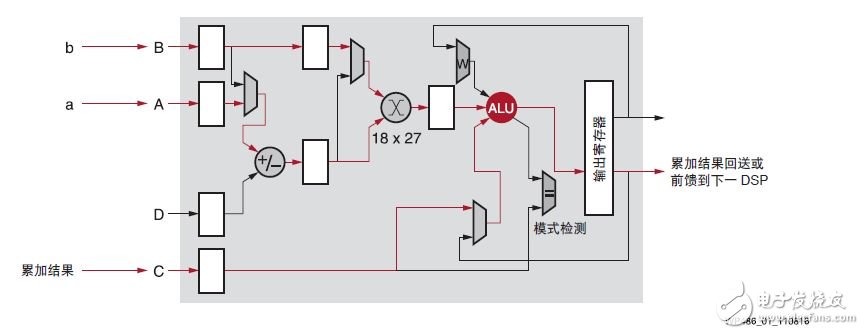

赛灵思的 DSP48E2 设计用于在一个时钟周期内高效地完成一个乘法累加算法, 多达 18x27 位的乘法和多达 48 位的累加,如图 1 所示。除了采用回送或链接多个 DSP Slice,乘法累加 (MACC) 也能使用赛灵思器件高效完成。

图 1 :使用 MACC 模式的 DSP Slice

在运行 INT8 计算时,较宽的 27 位宽自然占有优势。在传统应用中,预加法器一般用于高效实现 (A+B) x C计算,但这类计算在深度学习应用中很少见。将 (A+B) x C 的结果拆分为 A x C 和 B x C,然后在独立的数据流中进行累加,使之适用于典型深度学习计算的要求。

对 INT8 深度学习运算来说,拥有 18x27 位乘法器很占优势。乘法器的输入中至少有一个必须为最小 24位,同时进位累加器必须为 32 位宽,才能在一个 DSP Slice 上同时进行两个 INT8 MACC 运算。27 位输入能与 48 位累加器结合,从而将深度学习求解性能提升 1.75 倍(1.75:1 即为 DSP 乘法器与 INT8 深度学习 MACC 的比率)。其他厂商提供的 FPGA 在单个 DSP 模块中只提供 18x19 乘法器,DSP 乘法器与INT8 MACC 之比仅为 1:1。

可扩展的 INT8 优化目标是找到一种能够对输入 a、b 和 c 进行高效编码的方法,这样 a、b 和 c 之间的相乘结果可以容易地分解为 a x c 和 b x c。

在更低精度计算中,例如 INT8 乘法中,高位 10 位或 19 位输入用 0 或 1 填充,仅携带 1 位信息。对最终的 45 位乘积的高位 29 位来说,情况一样。因此可以使用高位 19 位开展另一计算,不会影响低位 8 位或16 位输入结果。

总的来说,要把未使用的高位用于另一计算必须遵循两条规则:

1. 高位不应影响低位的计算。

2. 低位计算对高位的任何影响必须可检测、可能恢复。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)