前言

DSP系统的引导装载是指在系统加电时,由DSP将一段存储在外部非易失性存储器中的代码移植到内部高速存储器单元并执行的过程。FLASH是一种高密度、非易失性的电可擦写存储器,而且单位存储比特的价格比传统EPROM要低。为此,本文介绍了TMS320C6713浮点DSP芯片和SST公司提供的SST39VF400A FLASH存储器的基本特点,给出了使用该FLASH存储器设计和实现完整的TMS320C6713 DSP引导装载系统的具体方法。

1 硬件设计

1.1 主要芯片介绍

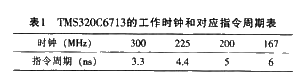

其次是精度高。TMS320C6713有三个因素影响着浮点格式的内在高精度。首先,浮点DSP的24位I/O字长在整数与实数值方面可实现比定点器件中常用的16位字长更高的精确度。第二.取幂大幅提高了应用可用的动态范围,较大的动态范围对处理极大数据集以及难以方便预计数据集范围的情况相当重要。第三,硬件内部的浮点数据表示法比定点器件更为精确,这就保证了最终结果的更高精确度。

SST39VF400A是SST公司推出的FLASH存储器。该器件十分适合用作外扩存储器,它的存储容量为4 MB,采用3.3 V单电源供电,因而无需额外提供高电压即可通过一些特殊的命令字序列来实现对各个子模块的读写和擦除。并可重复十万次以上,此外,还可通过DSP编程来实现对它的读写 *** 作,十分适合于系统的调试和开发。

1.2 系统硬件接口设计

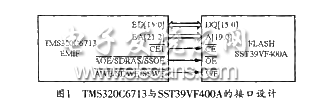

DSP访问片外存储器主要通过外部存储器接口(EMIF)完成。它不仅具有很强的接口能力(可以和各种存储器直接接口),而且具有很高的数据吞吐能力(高达1 200 MB/s)。TMS320C6713的EMIF能支持8位、16位和32位宽的所有存储器,当从这些窄位宽的存储空间读写数据时,EMIF会将多个数据打包成一个32位的值,而不必增加额外电路。TMS320C6713与SST39VF400的接口电路设计如图1所示。该电路主要通过DSP的相关输出管脚来控制FLASH的擦除和读写。其中,A0~A19为地址线,DQ0~DQ15为数据线,OE和WE分别为输出使能和写使能,CE1为片使能。由于TMS320C6713默认的引导模式是从外部CE1空间的16位FLASH来引导装载,所以,TMS320C6713的CE1和FLASH的片选CE相连。

2 软件设计

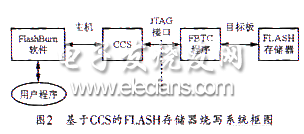

本引导装载系统主要由用户应用程序和FBTC (the FlashBurn Target Component)程序两部分构成,图2所示是基于CCS的Flash存储器烧写系统框图。其中,用户程序除了要完成用户设计要求外,还要对DSP板上的EMIF寄存器进行设置;FBTC程序则包括FLASH存储器烧写算法、初始化 *** 作、地址映射等。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)