核心提示:从工艺选择到设计直至投产,设计人员关注的重点是以尽可能低的功耗获得最佳性能。Altera在功耗和性能上的不断创新,那其28nm高端FPGA如何实现功耗和性能的平衡?具体有何优势?

从工艺选择到设计直至投产,设计人员关注的重点是以尽可能低的功耗获得最佳性能。利用Altera在功耗和性能上的不断创新,设计人员能够为他们的最终客户开发独具优势的高性能系统。特别是与其他高端FPGA相比,Altera的28nm高端FPGA功耗降低了15%,而性能却提高了1 个速率等级,更具有功耗优势。

Altera认识到,满足所有需求的方法并不适用于28nm节点。设计人员在其目标应用中需要合适的器件,因此,Altera为其高端FPGA选择了台积电公司(TSMC)的28nm高性能(28HP)工艺,在低成本和中端系列中采用了28nm低功耗(28LP)工艺。

为其StraTIx V FPGA选择了28HP工艺之后,Altera做出了几项开发选择以降低器件功耗。本文将介绍从工艺选择到工具以及建模的步骤,保证了在很有竞争力的电源布局下支持实现高性能。设计人员拥有合适的器件和工具,就能够以很低的功耗实现高性能,对设计进行较为精确的早期功耗估算。

功耗和性能考虑

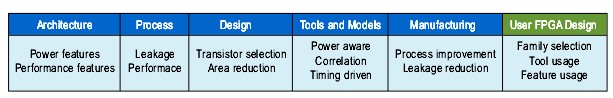

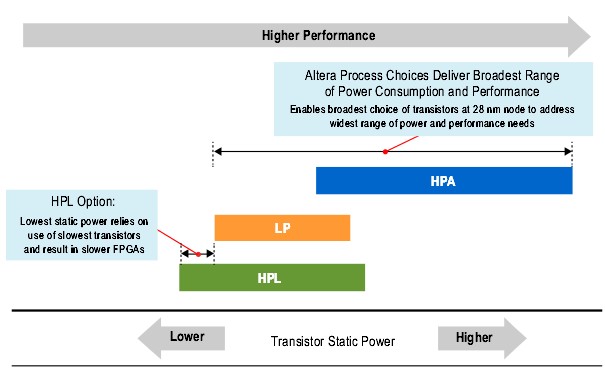

定义28nm高端器件的结构时,需要作出很多决定(参考表1),以尽可能低的功耗实现最佳性能。

表1 功耗和性能考虑

以低功耗实现高性能的结构

在过去几年中,低功耗技术越来越重要,在结构规划阶段就开始考虑降低功耗。Altera以前不断降低功耗的创新是可编程功耗技术及更多地使用了嵌入式硬核知识产权(IP)。在28nm节点,以低功耗实现高性能的新方法包括对于不使用的模块关断SRAM、低电压(0.85 V)结构以及部分重新配置功能等。

使用合适的工艺

工艺选择是Altera 28nm器件系列的关键考虑。如前所述,目标是帮助设计人员针对特定的目标市场和应用来定制功耗。在28nm系列产品上采用两种不同的半导体工艺,与前一代同类产品相比,Altera的28nm FPGA功耗降低了40%。

图1显示了TSMC提供的三种28nm工艺选择。在这些工艺中,大量晶体管具有较大的静态功耗范围。左侧的晶体管静态功耗较低,而右侧的较大。这也体现了静态功耗与这些晶体管性能之间的关系。总体上,晶体管性能越好,静态功耗也就越高。

图1 TSMC 28nm工艺选择

据TSMC资料,28HP工艺是使用高k金属门(HKMG)工艺技术的首选。28HP工艺具有优异的速度和性能,主要面向CPU、GPU、FPGA、PC、网络和消费类电子应用。在同样的漏电/电路门条件下,28HP工艺比40G工艺的速度提高了45%。

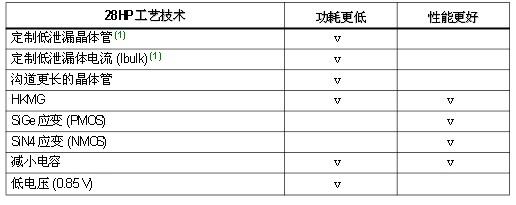

Altera选择TSMC 28HP HKMG工艺,借助与TSMC长达20年的合作关系,优化了StraTIx V FPGA低功耗工艺。表2详细介绍了Altera使用高性能工艺降低功耗的步骤。

表2 28HP工艺技术降低了功耗,提高了性能

说明:(1)专门提供仅供Altera 使用的工艺。

大部分TSMC客户必须使用标准工艺,而Altera与TSMC近20年的密切协作使得两家公司能够一起工作开发实现Altera的专用功能。对于28HP工艺,Altera采用可编程功耗技术,联合开发了定制低漏电晶体管和减小了器件体漏电。这两项功能与高性能晶体管相结合,可以调整每一设计模块,以尽可能低的功耗实现最合适的性能。

在28nm时代,Altera继续采用以前Altera获得专利的创新可编程功耗技术,不需要更多的FPGA设计投入,降低了静态功耗。 Altera的Quartus II开发软件在时间关键通路上应用可选的反向偏压,调整逻辑电压阈值,在需要的地方实现高性能,同时降低了所有其他逻辑的静态功耗。这种可调整能力保证了 StraTIx V FPGA设计人员降低了整个设计的静态功耗,同时实现了高性能。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)