我们为什么需要高层次综合

高层次综合(High-level Synthesis)简称 HLS,指的是将高层次语言描述的逻辑结构,自动转换成低抽象级语言描述的电路模型的过程。所谓的高层次语言,包括 C++、C++、SystemC 等,通常有着较高的抽象度,并且往往不具有时钟或时序的概念。相比之下,诸如 Verilog、VHDL、SystemVerilog 等低层次语言,通常用来描述时钟周期精确(cycle-accurate)的寄存器传输级电路模型,这也是当前 ASIC 或 FPGA 设计最为普遍使用的电路建模和描述方法。

然而,HLS 技术在近十年来获得了大量的关注和飞速的发展,尤其是在 FPGA 领域。纵观近年来各大 FPGA 学术会议,HLS 一直是学术界和工业界研究最集中的领域之一。究其原因,主要有以下几点。

第一,使用更高的抽象层次对电路建模,是集成电路设计发展的必然选择。集成电路伴随摩尔定律发展至今,其复杂性已经逐渐超过人类可以手工管理的范畴。例如,苹果 iPhone11 内置的 A13 芯片,就有着约 85 亿支晶体管。

然而,根据 NEC 2004 年发布的研究,一个拥有 100 万逻辑门的芯片设计通常需要编写 30 万行 RTL 代码。因此,完全使用 RTL 级的逻辑抽象设计当代芯片是不现实的,并将对设计、验证、集成等各个环节造成巨大的压力。

相比之下,使用诸如 C、C++等高层语言对系统建模,可以将代码密度压缩 7 到 10 倍,这极大的缓解了设计复杂度。

第二,高层语言能促进 IP 重用的效率。传统的基于 RTL 的 IP 往往需要定义固定的架构和接口标准,在 IP 重用时需要花费大量时间进行系统互联和接口验证。相比之下,高层语言隐藏了这些要求,转而由 HLS 工具负责具体实现。

对于 FPGA 而言,现代 FPGA 里有着大量成熟的 IP 单元,如嵌入式存储器、算术运算单元、嵌入式处理器,以及最近逐渐兴起的 AI 加速、片上网络系统等等。这些 FPGA IP 有着固定的功能和位置,因此可以被 HLS 工具充分利用,在提升 IP 重用效率的同时,简化综合算法、提高综合后电路的性能。

第三,HLS 能帮助软件和算法工程师参与、甚至主导芯片或 FPGA 设计。这是由于 HLS 工具能封装和隐藏硬件的实现细节,从而使软件和工程师能专注于上层算法的实现。对于硬件工程师而言,HLS 也能帮助他们进行快速的设计迭代,并专注于对性能、面积或功耗敏感的模块和子系统的优化设计。

FPGA 高层次综合的前世今生

伴随集成电路的复杂性的飞速增长,芯片设计方法学也在不断演进。早在 FPGA 出现之前,人们就已经开始尝试摆脱依靠人工检视芯片版图的设计方法,转而探索使用高层语言对电路逻辑进行行为级描述,并通过自动化工具将电路模型转化为实际的电路设计。

在上世纪八九十年代,面向集成电路设计的 HLS 工具就已经是学术界研究的热点。这其中比较有代表性的工作,包括卡耐基梅隆大学的 CMU-DA(design automaTIon)工具,以及加拿大卡尔顿大学提出的 force-directed 调度算法等等。

从现在看来,这些工作为当前的电路综合算法打下了基础,并为后来 HLS 研究提供了很多宝贵的经验和借鉴。然而,这个阶段的 HLS 工作在成果转化方面十分失败,并未有效的转化成工业实践。一个最主要的原因,就在于“在错误的时间,遇上了对的人”。

当时正值摩尔定律蓬勃兴起的时期,集成电路设计正在经历史上最大的变革。在后端,自动布局布线已经逐渐成为主流;在前端,RTL 综合也在逐渐兴起。传统电路设计工程师都纷纷开始采用基于 RTL 的电路建模方法,取代传统的基于原理图和版图的设计,并由此带来 RTL 综合工具的飞速发展。相比之下,这个阶段的 HLS 研究往往使用了特殊的编程语言,如 CMU-DA 采用的名为“ISPS”的语言,因此很难获得那些正在和 RTL 处于“蜜月期”的工程师们的青睐。

伴随着一段时间的沉寂,HLS 在 2000 年之后再次开始获得学术界和工业界的关注,比较有名的工具包括 Bluespec 和 AutoPilot 等。主导这一变化的主要原因是,HLS 工具开始将 C/C++作为主要的目标语言,从而被很多不了解 RTL 的系统和算法工程师所逐渐接受。同时,HLS 工具综合生成的结果也有了长足进步,在某些应用领域甚至可以和人工手写 RTL 近似的性能水平。

此外,FPGA 的逐渐兴起也对 HLS 的发展起到了重要的助推作用。和 ASIC 设计不同,FPGA 有着固定数量的片上逻辑资源。因此 HLS 工具不用过度纠结于 ASIC 设计中面积、性能和功耗的绝对优化,而只需要将设计合理的映射到 FPGA 的固定架构上即可。这样,HLS 就成为了在 FPGA 上快速实现目标算法的绝佳方式。

时至今日,高层次综合技术取得了进一步的发展。大型 FPGA 公司都推出了各自的 HLS 工具,如赛灵思的 Vivado HLS 和英特尔的 HLS 编译器、OpenCL SDK 等。在学术界也有诸多成果涌现,如多伦多大学的 LegUp 等等。

接下来,老石将以 AutoPilot 这个 HLS 工具为例,简单介绍高层次综合的主要工作原理。

高层次综合的主要工作原理

AutoESL 公司的 AutoPilot 工具,可以说是 HLS 领域最为成功的学术成果转化案例。AutoPilot 源自于 UCLA 丛京生教授主导的 xPilot 项目,从随后与当时负责该课题的博士生张志如(现任康奈尔大学副教授)一起创办了 AutoESL 公司,并在 2011 年被赛灵思收购,成为了之后的 Vivado HLS。

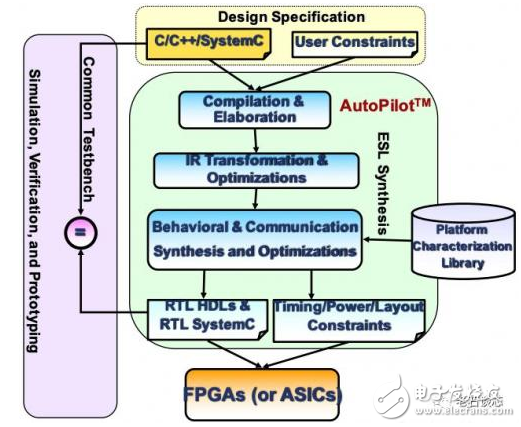

AutoPilot 的工作流程框图如下图所示。在前端,它使用了基于 LLVM 的编译器架构,能够处理可综合的 ANSI C、C++,以及 OSCI SystemC 等语言编写的模型。这个名为 llvm-gcc 的前端编译器会将高层语言模型转换为中间表达式(IR),并进行一系列针对代码复杂度、冗余、并行性等方面的代码优化。然后再根据具体的硬件平台,综合生成 RTL 代码、验证与仿真环境,以及必须的时序和布局约束等。

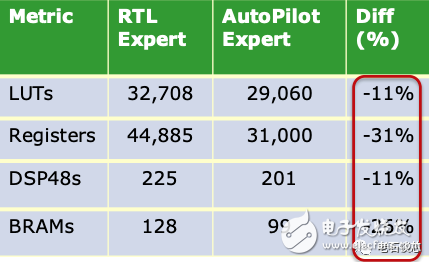

AutoPilot 的成功之处在于,它的 HLS 结果在某些应用领域完胜人工优化 RTL 取得的结果。例如,在一个无线 MIMO 系统中使用的 Sphere 解码器 IP 中,AutoPilot 将 4000 行 C 代码算法成功综合到 Virtex5 FPGA 上,运行在 225MHz,并取得了比赛灵思 Sphere 解码器 IP 更少的逻辑资源使用量,见下图。这个结果放在现在也令人十分震撼,它很好的证明了 HLS 有潜力取得比 RTL IP 更为出色的性能。

高层次综合工具常用的优化方法

传统的处理器编译器设计通常只有一个主要目标,那就是尽量提升性能。相比之下,高层次综合工具需要统筹考虑各种电路设计的主要指标,如性能、功耗、面积等等,同时也要兼顾工具本身的性能,比如占用的资源和运行时间等。因此,在开发 HLS 工具时,要额外考虑和采用更多的优化方法,而这些优化方法也是当今学术界和工业界在 HLS 领域重点研究的方向。总的来说,HLS 工具的主流优化方法有以下几种。

01

字长分析和优化

FPGA 的一个最主要特点就是可以使用任意字长的数据通路和运算。因此,FPGA 的 HLS 工具不需要拘泥于某种固定长度(如常见的 32 位或 64 位)的表达方式,而可以对设计进行全局或局部的字长优化,从而达到性能提升和面积缩减的双重效果。

然而,字长分析和优化需要 HLS 的使用者对待综合的算法和数据集有深入的了解,这也是限制这种优化方式广泛使用的主要因素之一。

02

循环优化

循环优化一直是 HLS 优化方法的研究重点和热点,因为这是将原本顺序执行的高层软件循环有效映射到并行执行的硬件架构的重点环节。

循环优化的最终目的,就是尽量将循环里两次相邻的 *** 作以最小的时延实现,理想情况下,相邻的循环 *** 作可以完全并行执行。然而,由于硬件资源的限制,以及更多的是因为循环间存在嵌套和依赖关系,很难将循环完全展开。如何优化各种循环,以实现最优的硬件结构,就成为了学术界和工业界最为关心的要点。

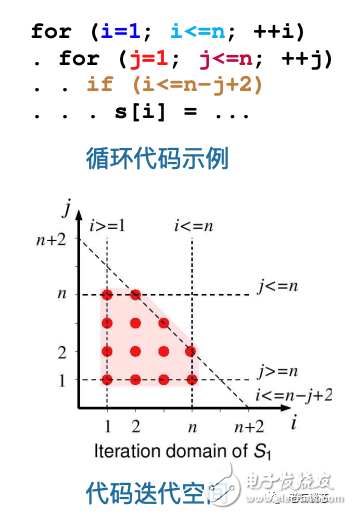

一个流行的循环优化方法,就是所谓的多面体模型,即 Polyhedral Model。多面体模型的应用非常广泛,在 HLS 里主要被用来将循环语句以空间多面体表示(见下图),然后根据边界约束和依赖关系,通过几何 *** 作进行语句调度,从而实现循环的变换。

需要指出的是,多面体模型在 FPGA HLS 里已经取得了相当的成功,很多研究均证明多面体模型可以帮助实现性能和面积的优化,同时也能帮助提升 FPGA 片上内存的使用效率。

03

对软件并行性的支持

C/C++与 RTL 相比,一个主要的区别是,前者编写的程序被设计用来在处理器上顺序执行,而后者可以通过直接例化多个运算单元,实现任务的并行处理。随着处理器对并行性的逐步支持,以及如 GPU 等非处理器芯片的兴起,C/C++开始逐渐引入对并行性的支持。例如,出现了 pthreads 和 OpenMP 等多线程并行编程方法,以及 OpenCL 等针对 GPU 等异构系统进行并行编程的 C 语言扩展。

因此作为 HLS 工具,势必要增加对这些软件并行性的支持。例如,LegUp 就整合了度 pthreads 和 OpenMP 的支持,从而可以实现任务和数据层面的并行性。

另外,Altera 在被英特尔收购之前就已经推出了 OpenCL SDK,可以将 OpenCL 进行高层次综合,并生成 FPGA 电路逻辑与 CPU 代码两部分,从而实现 FPGA 作为硬件加速模块的快速开发。

高层次综合的发展前景

HLS 经过十数年的发展,虽然有诸如 AutoPilot、OpenCL SDK 等 FPGA HLS 商业化成功的案例出现,但距离其完全替代人工 RTL 建模还有很长的路要走。

比如,对于 FPGA 而言,内存瓶颈一直是制约系统性能的重要因素。除片上的各类 BRAM 之外,还有各类片外存储单元,如 DDR、QDR,以及近年兴起的 HBM 等等。因此,有效利用片上和片外各类存储单元一直是 HLS 的研究热点。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)