概述

对于硬件加速模块来说,这些硬件加速模块会消耗源于CPU存储器的数据,并且以streaming方式产生数据。本文使用Vivado HLS和xfft IP模块(在IP Integrator使用HLS IP那节用过)。这些模块是连接到HP0的AXI4从端口,使得zynq7处理系统的数据通过AXI DMA IP核。硬件加速模块是免费的运行,并不需要驱动,只要数据被CPU推送(通常简称为处理系统或PS)。这里还要强调软件要求避免缓存一致性问题。

在Zynq CPU和HLS加速模块之间Streaming Data

Step 1: 产生HLS IP

这里会产生两个Vivado HLS文件,即fe_vhls_prj和be_vhls_prj,它们都包含HLS IP。

Step 2: 创建Vivado Project

打开Vivado,选择Create New Project,下一步在Project locaTIon里选择lab2文件夹,并将project name命名为project_1,然后选择RTL Project和do not specify sources at this TIme,在Board选择ZYNQ-7 ZC702 EvaluaTIon Board,最后点击Finish。

Step 3: 给IP库里添加HLS IP

在Flow Navigator窗口点击IP Catalog,然后选择IP SetTIngs,在IP Settings对话框选中Add Repository,在lab2下Create New Folder,并命名为vivado_ip_repo,然后依次添加lab2/hls_designs/fe_vhls_prj/IPXACTExport/impl/ip和lab2/hls_designs/be_vhls_prj/IPXACTExport/impl/ip,现在在HLS IP中有Hls_real2xfft和 Hls_xfft2real这两个IP。

Step 4: 创建顶层模块设计

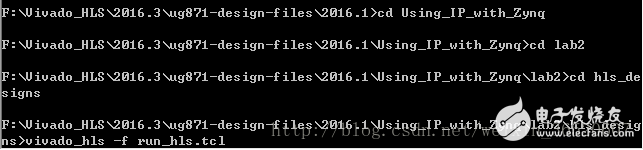

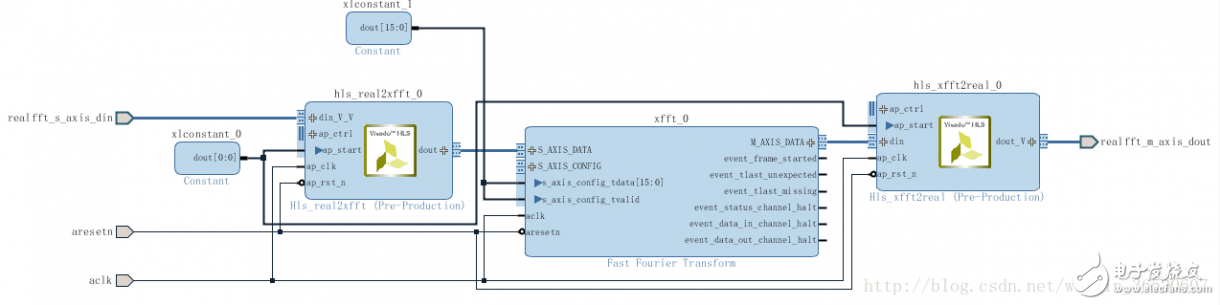

2.添加Hls_real2xfft和 Hls_xfft2real这两个IP,然后将HLS blocks 和 FFT block连接起来,这里即将hls_real2xftt模块的dout接口跟FFT模块的S_AXIS_DATA接口,以及hls_xfft2real模块的din接口跟FFT模块的M_AXIS_DATA接口连接起来,最后按Ctrl+A,给所有模块Create Hierarchy,并命名为RealFFT,并确认Move ‘3’ selected blocks to new hierarchy被选中。

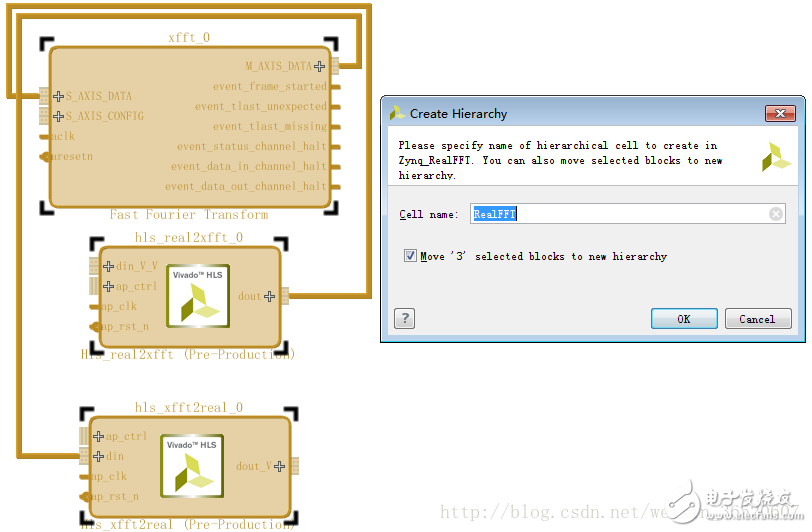

3.下面给RealFFT hierarchical block添加pins,双击RealFFT打开block,右击hls_real2xfft_0模块的din_V_V端口,并选择Create Interface Pin,并命名为realfft_s_axis_din(其他默认),同理给hls_real2xfft模块的ap_clk端口Create Pin,并命名为aclk,同理给hls_xfft2real模块的dout_V端口Create Pin,并命名为realfft_m_axis_dout,同理给ap_res_n端口Create Pin,并命名为aresetn。

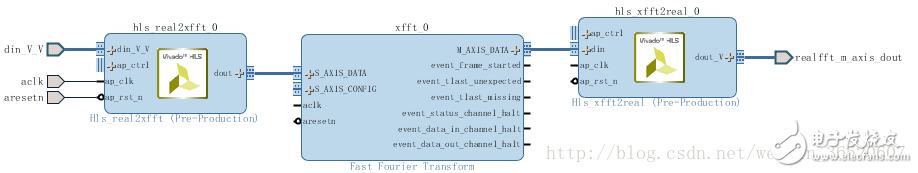

4.右键Add IP输入const,双击xlconstant_0模块确认Const Val设置为1,展开所有的ap_ctrl端口,将所有的ap_start端口跟xlconstant_0的输出端口连接,然后分别连接所有aclk和aresetn端口,添加一个新的xlconstant,这里将Const Width设置为16,将Const Val设置为0,展开S_AXIS_CONFIG端口,最后将s_axis_config_tdata 和s_axis_config_tvalid跟新的xlconstant模块连接,如下图

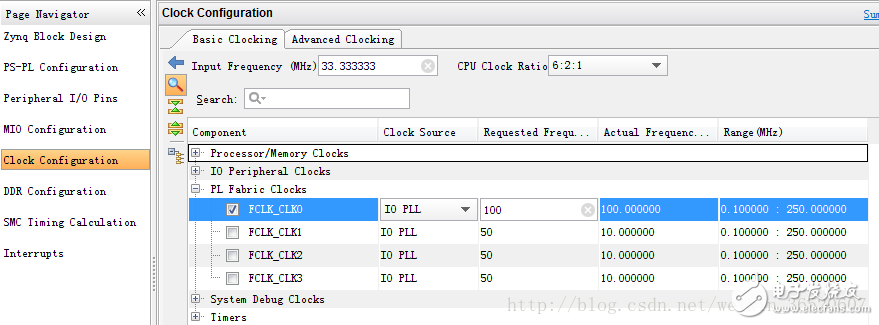

5.添加ZYNQ7 Processing System IP,并点击Run Block Automation,然后双击processing_system7_0模块,点击Presets,并选择ZC702开发板,然后点击PS-PL Configuration,展开HP Slave AXI Interface,选中并确认S AXI HP0 interface下的S AXI HP0 DATA WIDTH为64,最后选择Clock Configuration,展开PL Fabric Clocks,将要求的频率改为100MHz。

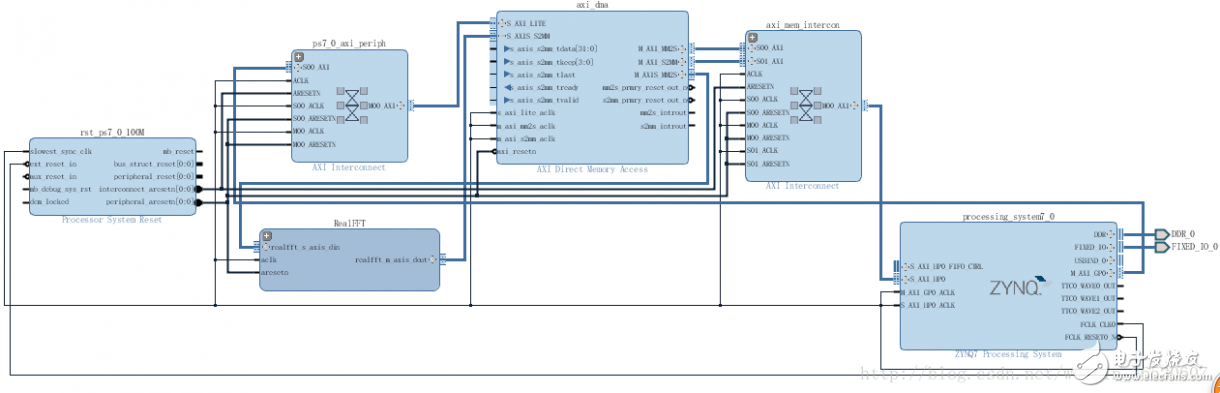

6.将RealFFT模块的realfft_s_axis_din端口跟Zynq AP SoC模块的S_AXI_HP0端口连接,此时会出现三个小模块,分别是AXI DMA core, AXI Interconnect和 Processor System Reset block,再将RealFFT模块的realfft_m_axis_dout跟S_AXI_HP0连接,然后点击Run Connection Automation,再将RealFFT模块的aclk和aresetn端口分别连接到processing_system7_0的FCLK_CLK0端口和rst_processing_system7_0_100M的peripheral_aresetn端口,最后run Validate Design。

Step 5: 实现系统

在进行系统设计之前,必须生成implementation sources,并且创建一个HDL wrapper,来用于综合和实现的顶层模块。

在这里点击Project Manager,右键Zynq_ RealFFT选择Generate Output Products,去生成必要的源文件,再次右键Zynq_RealFFT选择Create HDL Wrapper,此时顶层设计变成Zynq_ RealFFT _wrapper.v,然后Generate Bitstream,最后在位流文件生成后的窗口里,选择Open Implemented Design并点击OK。

Step 6:打开 SDK去测试 ZYNQ 系统

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)