如何利用电容式数字隔离器进行设计

目前,有关电子设备使用和设计的安全规定层出不穷,使电流隔离器几乎成为所有数据采集和传输系统中的必需。避免控制系统低压电路在电场中遭受潜在的传感器和传动器组件高压损害的一种方法,就是使用数字隔离器。

本文的目的在于告诉大家如何简化隔离系统设计,文章除描述电容式数字隔离器的基本功能,详细介绍如何在信号通路中安装隔离器外,还就如成功设计电路板提供了一些有价值的参考意见。

电容式数字隔离器的基本功能

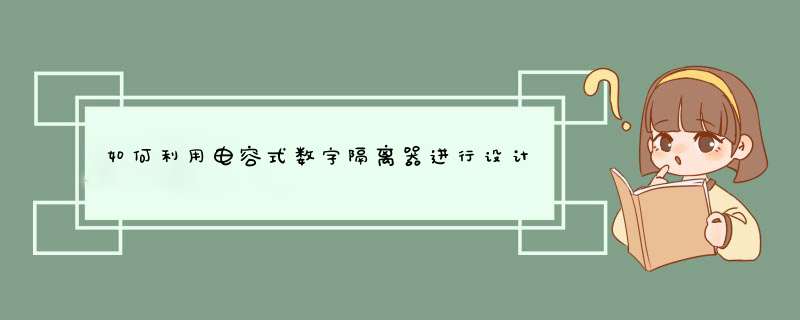

图1显示了一个电容式数字隔离器的简化结构图,该隔离器由一个高速信号路径和一个低速信号路径组成。高速路径(蓝色部分)传输100kbps至150Mbps的信号,而低速路径(橙色部分)则传输100kbps以下信号至dc。

图 1 电容式数字隔离器的简化结构图

蓝色部分所示路径中处理的高速信号被电容式隔离势垒分为多个快速瞬变脉冲群。随后的触发器(FF)将这些瞬态脉冲群转换成波形和相位均与输入信号一致的脉冲。内部看门狗(WD)检查高速信号边缘的周期性。在低频输入信号情况下,连续信号边缘间的持续时间超出了看门狗窗口。这样便迫使看门狗将输出开关位置从高速路径(位置1)改变为低速路径(位置2)。

低速路径比高速路径多出几个功能元件。因为低频输入信号要求隔离势垒禁止采用大电容,所以输入信号被用于对内部振荡器(OSC)的载波频率进行脉宽调制(PWM)。这就构成了一个非常高的频率,能够通过该电容势垒。由于输入得到了调制,因此必须在实际数据传输至输出端以前使用低通滤波器(LPF)去除其中的高频载波。

在信号链中的安装位置

数字隔离器分为单通道、双通道、三通道及四通道器件,可以实现单向和双向运行,它们的共有特性如下:

- 不符合任何特定接口标准;

- 使用3V/5V逻辑开关技术

- 专为电隔离数字、单端(SE)数据线而设计

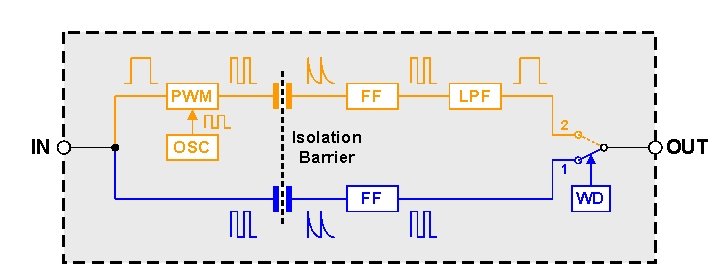

虽然最后一点似乎是设计上的限制,然而图2却显示了如何对多种接口进行隔离,其中包括低压 SPI、高压RS232、差分USB和差分CAN/RS485。

图 2 数字隔离器必须安装在隔离接口的单端部分中

所有接口都有一个相同点,那就是数字隔离器必须安装在隔离接口的单端3V/5V部分。

由于数字隔离器都具有1到2ns的升降时间,因此它们在长信号走线情况下往往易出现信号反射,其特性阻抗与隔离器输出的源阻抗不匹配。因此,我们建议在其相应数据接收装置和数据源(例如:控制器、驱动器、接收器和收发器等)附近安装一个隔离器。在设计中如果无法这样做,那么就必须使用受控的阻抗传输线。

PCB 设计指南

就数字电路板而言,要使用标准FR-4环氧玻璃作为PCB材料,这是由于相比那些廉价材料,其不但符合UL94-V0要求,而且还拥有更少的高频介电损耗、更低的吸湿性、更大的强/硬度以及更高的阻燃特性。

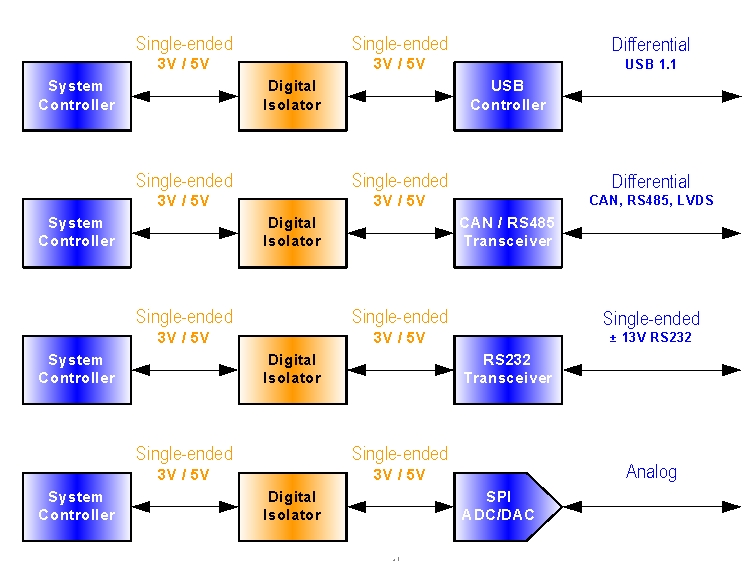

要实现低电磁干扰(EMI)的PCB设计,这里推荐一个最少四层的设计实例(请参见图3),其从上到下分别为:高速信号层、接地层、电源层以及低频信号层。

图 3 推荐的四层板叠层

在顶层布置高速走线为隔离器及其相应的驱动器提供了一目了然的连接。高速走线要短,并避免使用过孔,以此保证高速走线电感最低。

紧接着高速信号层放置一个平衡板面地线层,以确保接地层和信号走线之间存在强大的电气耦合。这样便建立起传输线互联的受控阻抗,同时也极大地减少了EMI。最终,平衡板面地线层为回流提供了一个非常好的低电感路径。

将电源层置于接地层下面。这两个参考层构成了一个大约为100pF/in2的附加高频旁路电容器。

在底层布线低速控制信号。这些信号链路拥有足够的余量来承受过孔引起的中断,从而实现了更大的灵活性。

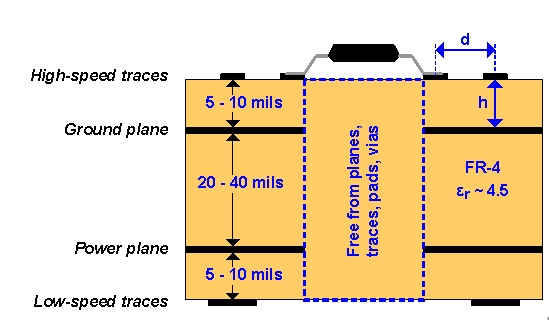

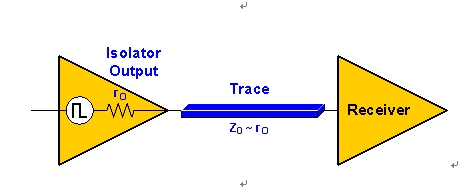

受控阻抗传输线是特性阻抗Z0始终受控于其几何特性的走线。走线长度大于15mm(tr=1ns)和 30mm(tr=2ns)时,走线阻抗必须要与隔离器输出阻抗Z0~rO匹配(如图4所示),使信号反射最小化。这被称为源阻抗匹配。

图 4 源阻抗匹配:Z0 ~ rO

隔离器的动态输出阻抗r0,可以通过隔离器数据手册中列出的近似电压-电流输出特性线性部分得到。一般来说,标准输出阻抗大约为70Ω。因此,对一条标准的2盎司镀铜线和电介质为4.5的FR-4而言,接地层上8mm宽、10mm长的走线几何形状会产生所需的70Ω特性阻抗。

布线指南

建议遵循下列几条主要的布线原则,以保持信号完整性和低EMI。

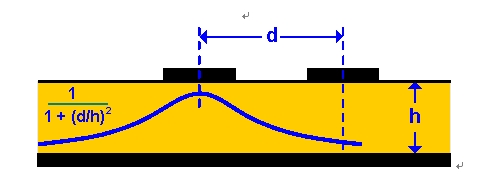

为了将串扰降至10%以下,需保持信号走线是高速信号层到接地层距离的三倍(d=3h)。信号走线下的回流密度遵循1/[1+(d/h)2]函数,因此其在d>3h点上的密度会非常低,从而避免邻近走线中出现较大的串扰(请参见图5)。

图 5 利用 d = 3h 来最小化串扰

使用45o走线弯曲(或者斜切式弯曲)而非90o弯曲,可保持有效的走线阻抗并避免信号反射。

为了实现在噪声环境下的工作,将隔离器的闲置启动输入通过一个电阻器(1kΩ到10kΩ)连接到合适的参考层。将高电平有效、高位允许输入连接到电源层,同时将低电平有效输入连接至接地层。

当过孔电感增加信号路径电感时,要避免各层随快速信号走线改变。

将大容量电容(比如10μF)置于靠近电源如稳压器旁,或是在电源进入PCB的地方。

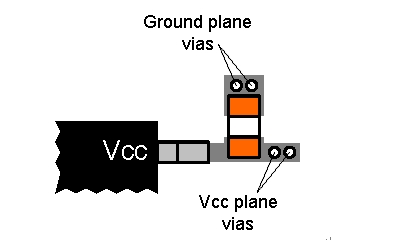

通过将电容的电源端直接连接至器件的电源端,然后经过孔连至Vcc层,在器件上安装小容量的0.1μF或0.01μF旁路电容。经数个过孔将电容接地端连接至接地层(请参见图6)。

图 6 将旁路电容直接连接至 Vcc 终端

将多个过孔用于连接旁路电容和其他保护器件(例如:瞬态电压抑制器和齐纳二极管),从而最小化接地连接的过孔电感。

总结

尽管关于PCB设计的资料有很多,但本文主要提供一些涉及数字隔离器电路板设计的建议。遵循这些建议将有助于在最短的时间内完成一个符合EMC标准要求的电路板设计。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)