分立元件门电路虽然结构简单,但是存在着体积大、工作可靠性差、工作速度慢等许多缺点。1961年美国德克萨斯仪器公司率先将数字电路的元器件和连线制作在同一硅片上,制成了集成电路。由于集成电路体积小、质量轻、工作可靠,因而在大多数领域迅速取代了分立元件电路。随着集成电路制作工艺的发展,集成电路的集成度越来越高。

TTL信号是数字信号.CMOS传输门(Transmission Gate)是一种既可以传送数字信号又可以传输模拟信号的可控开关电路。

按照集成度的高低,将集成电路分为小规模集成电路、中规模集成电路、大规模集成电路、超大规模集成电路。根据制造工艺的不同,集成电路又分为双极型和单极型两大类。TTL门电路是目前双极型数字集成电路中用的最多的一种。

TTL门电路中用的最普遍的是与非门电路,下面以TTL与非门为例,介绍TTL电路的基本结构、工作原理和特性。

(1)TTL与非门的基本结构

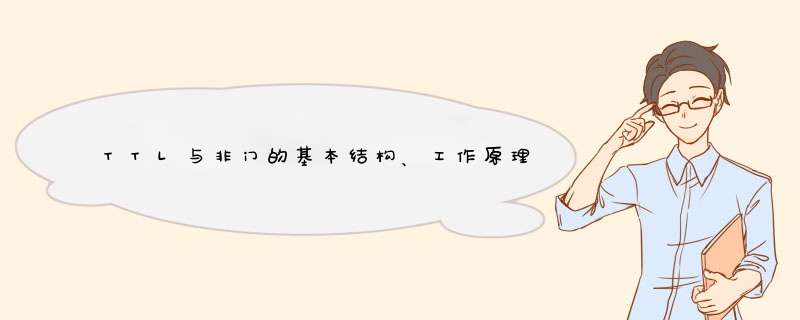

图1是TTL与非门的电路结构。可以看出,TTL与非门电路基本结构由3部分构成:输入级、中间级和输出级。因为电路的输入端和输出端都是三极管结构,所以称这种结构的电路为三极管---三极管逻辑电路。

图1 TTL与非门电路的基本结构

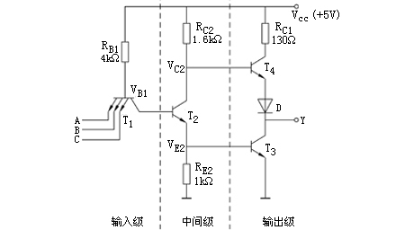

输入级:输入级是一个与门电路结构。T1是多发射极晶体管,可以把它的集电结看成一个二极管,把发射结(三个发射结)看成是与前者背靠背的3个二极管,如图2所示。由此看出,输入级就是一个与门电路:Y=A·B·C。

(a)多发射极晶体管(b)多发射极晶体管的等效二级管电路

图2 多发射极晶体管的等效电路

中间级:由三极管T2和电阻RC1、RE2组成。在电路的开通过程中利用T2的放大作用,为输出管T3提供较大的基极电流,加速了输出管的导通。所以,中间级的作用是提高输出管的开通速度,改善电路的性能。

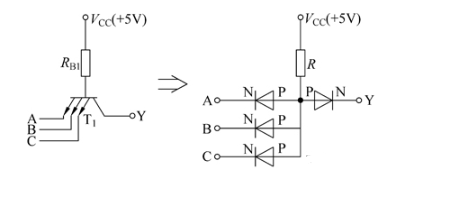

输出级:由三极管T3、T4、二极管D和电阻RC4组成。如图3所示,图3(a)是前面讲过的三极管非门电路,图3(b)是TTL与非门电路中的输出级。从图中可以看出,输出级由三极管T3实现逻辑非的运算。但在输出级电路中用三极管T4、二极管D和RC4组成的有源负载替代了三极管非门电路中的RC,目的是使输出级具有较强的负载能力。

图3 晶体管非门电路与TTL与非门输出级

(2)工作原理

在下面的分析中假设输入高、低电平分别为3.6V和0.3V,PN结导通压降为0.7V。

①输入全为高电平3.6V(逻辑1)

如果不考虑T2的存在,则应有UB1=UA+0.7=4.3V。显然,在存在T2和T3的情况下,T2和T3的发射结必然同时导通。而一旦T2和T3导通之后,UB1便被钳在了2.1V(UB1=0.7×3=2.1V),所以T1的发射结反偏,而集电结正偏,称为倒置放大工作状态。由于电源通过RB1和T1的集电结向T2提供足够的基极电位,使T2饱和,T2的发射极电流在RE2上产生的压降又为T3提供足够的基极电位,使T3也饱和,所以输出端的电位为UY=UCES=0.3V, UCES为T3饱和压降。

可见实现了与非门的逻辑功能之一:输入全为高电平时,输出为低电平。

②输入低电平0.3V(逻辑0)

当输入端中有一个或几个为低电平0.3V(逻辑0)时,T1的基极与发射级之间处于正向偏置,该发射结导通,T1的基极电位被钳位到UB1=0.3+0.7=1V。T2和T3都截止。由于T2截止,由工作电源VCC流过RC2的电流仅为T4的基极电流,这个电流较小,在RC2上产生的压降也小,可以忽略,所以UB4≈VCC=5v,使T4和D导通,则有:UY=VCC-UBE4-UD=5-0.7-0.7=3.6V。

可见实现了与非门的逻辑功能的另一方面:输入有低电平时,输出为高电平。

综合上述两种情况,该电路满足与非的逻辑功能,是一个与非门。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)