谈起FPGA的结构,通常人们是这样认为的:FPGA的基本结构是由大量的相对较小的可编程逻辑块“岛”镶嵌在可编程互连的“海”里面构成的。初看起来感觉有点云里雾里,仔细琢磨一下,文艺范的表达确实是那么回事:

目前市场上90%以上的FPGA来自于xilinx和altera这两家巨头,而这两家FPGA的实现技术都是基于SRAM的可编程技术,FPGA内部结构基本一致,所以本文仅以xilinx的7系列FPGA介绍。

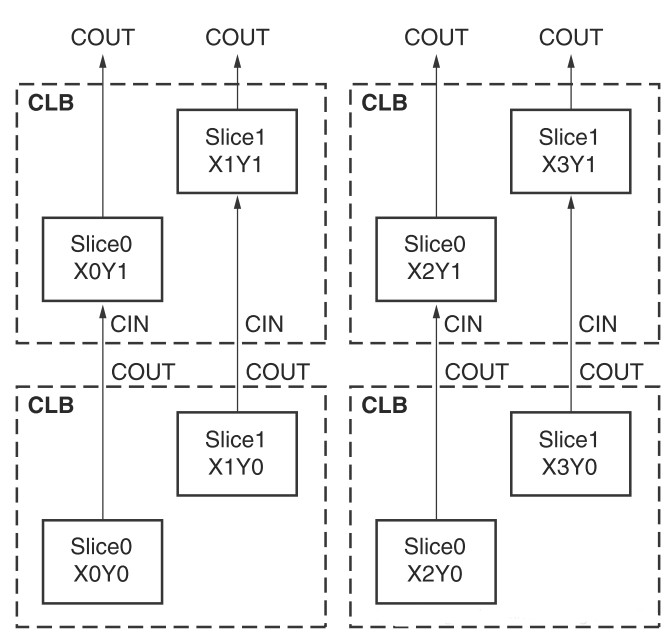

CLB是xilinx FPGA基本逻辑单元,每个CLB包含两个slices,每个slices由4个6输入LUT(查找表)和8个D触发器组成。同一CLB中的两片slices没有直接的线路连接,分属于两个不同的列。每列拥有独立的快速进位链资源。让我们来看看基本逻辑单元CLB的结构,如图1所示列出了4个CLB:

图1:CLB结构

整个FPGA内部的基本结构就是由成千上万个这样的CLB组成的,CLB与CLB之间存在大量的信号互连线,作为数据流动的通道。开篇说的“岛”就是CLB,“海”就是信号互连线。当然,这只是最基本的FPGA结构,实际的FPGA内部“大海”里还得镶嵌其它的“明珠”才能正常工作,比如时钟模块、存储器、网络模块、收发器模块等等,“明珠”数量越多,FPGA功能就越丰富、当然价格也越贵。

那么,大家可能有疑惑,CLB怎么就能实现复杂的数字逻辑功能呢?别忘了上文交代了1个CLB包含2个Slice,每个Slice又由4个6输入LUT、8个D触发器以及多个MUX组成。简单来说,LUT是查找表,可以实现数字逻辑中的组合逻辑功能,比如C=A+B;D触发器则实现时序逻辑功能;MUX则增强Slice内部信号流通的灵活性。

也就是说1个Slice内部就可以灵活的实现组合逻辑和时序逻辑,那么1个CLB(等于2个Slice)呢?成千上万个CLB呢?所以FPGA就可以实现很复杂的数字运算了。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)