载荷图像可视化是深空探测任务中的重要需求,但受信道带宽的限制,无法实时传输所有载荷数据,因此星载复接存储器中图像的抽取下传是实现任务可视化的关键。

本文设计了一种载荷图像抽取方法,适用于深空探测航天器载荷自主管理和可视化应用。通过图像帧识别、指针管理和数据筛选实现图像抽帧回放算法,具有图像完整、实时,速率自适应的特点。该方法在某探测器工程项目中采用FPGA进行了实现,经测试、试验验证,满足工程可视化要求。

0 引言

随着深空探测任务需求的发展,星上数据流呈现复杂化、多样化,对在轨数据处理的需求迅速增长,地面可视化是深空探测工程任务的重要需求之一,在轨图像的存储和实时抽取下传是解决可视化需求的关键。实际工程中,图像数据量与下行速率之间存在矛盾,工程应用上需要获取高分辨率的载荷图像导致了数据速率的增加,而深空探测受数传信道距离和速率的限制,无法实时下传全部数据。因此需要在星载复接存储器中对图像进行处理,存储图像数据的同时对图像进行整帧抽取,下传最新的图像,实现任务可视化。星载复接存储器的功能是将多路不同格式的载荷数据按照高级在轨系统协议格式形成一路数据流,经过切分、组帧形成多个虚拟信道数据单元(VCDU),存入大容量存储芯片(FLASH),同时将大容量存储芯片中的数据按照选定地址进行回放,并根据需求对回放数据进行筛选。

针对上述需求,在星载复接存储器的存储回放过程中通过图像帧识别、指针管理、数据筛选实现抽取速率自适应的载荷图像抽取方法,并通过FPGA进行实现和验证,可为后续深空探测载荷数据管理任务提供技术参考。

1 抽帧回放算法

星载复接存储器的功能为复接多路载荷图像数据,将复接后的数据流存入大容量存储器,根据回放指令将固存中数据读出,进行信道编码后输出至数传。

抽帧回放的过程应结合复接存储器的工作过程,由于一幅图像数据量较大,复接器入口无法缓存整幅图像,因此综合考虑软硬件开销,设计在记录时进行数据标记,抽取在存储之后的回放过程中完成。

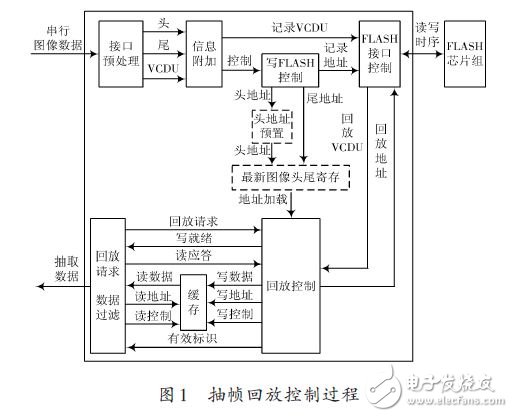

抽取方法如图1所示,图像通过LVDS接口以串行形式输入,在接口预处理模块,将一幅图像切分并填充为多个虚拟信道数据单元(VCDU),用于存储和下传。

同时利用跟随的门控信号判定图像数据的头尾,产生图像帧头、帧尾标识信号,以标识一幅完整的图像。信息附加模块将头尾标识信号组织成附加信息,填入数据内。

为了保证回放的图像总是最新的图像数据,需要知道最新图像的帧头VCDU 地址及帧尾VCDU 的存储地址。因此在记录过程中,使用一个最新图像数据帧地址寄存器来记录存储器中最新图像的帧头帧尾VCDU地址,每收完一幅完整的图像数据立即更新最新图像数据帧地址寄存器中的地址信息,保证最新图像数据帧地址寄存器中的地址为最新图像数据的帧头帧尾VCDU地址。

回放时,收到数据请求信号,回放控制模块从最新图像数据帧地址寄存器中加载最新图像地址,从此地址处依次回放,直到遇到了有尾帧标记字节的数据帧,完成一幅图像的抽取回放,之后继续加载最新图像数据帧地址寄存器,进行下一幅图像回放。

由于采用数据复接设计,多路图像会同时进入存储器,以多种VCDU 的形式存在,FLASH 的页 *** 作导致每次回放出的数据为两个VCDU,因此在备用符号域中设计附加信息,通过对附加信息的判读滤除多余数据,保证回放数据中充满有效抽取图像。

回放的速率取决于下行信道的速率,工程中由上级的回放请求信号控制。在每次请求到来时,均加载预先存入的最新图像地址,既保证了图像实时性,又达到了抽取速率自适应的要求。

抽帧回放算法主要考虑三个方面:抽取图像为完整的载荷图像数据;当前抽取出的图像为最新数据;抽取算法对抽取速率自适应。

1.1 完整性设计

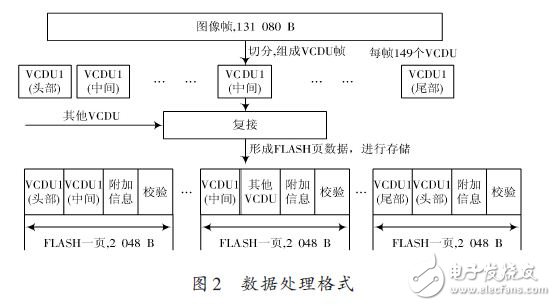

输入图像数据由接口模块生成VCDU,不同载荷数据通过VCID 被区分为不同类的VCDU,由于FLASH 采用页 *** 作模式,一页的大小为2 KB,设计中一页包含两个VCDU.

FLASH的读写都基于页进行 *** 作,读出一页的两个VCDU中,有多种可能性,数据处理过程如图2 所示,图2中给出三种可能,一是前一个是需要抽取的头数据,后一个是需要抽取的中间数据;二是前一个是需要抽取的图像数据,后一个是不需要抽取的其他 VCDU 数据;三是前一个是需要抽取的尾数据,后一个是下一幅图像的头,但不需要抽取。

可见,在抽取回放中必须滤除一定数据,保证抽取图像的完整性和正确性,因此在存储时增加附加信息,以解决图像完整性问题。

附加信息设计为6 b,格式定义见表1.

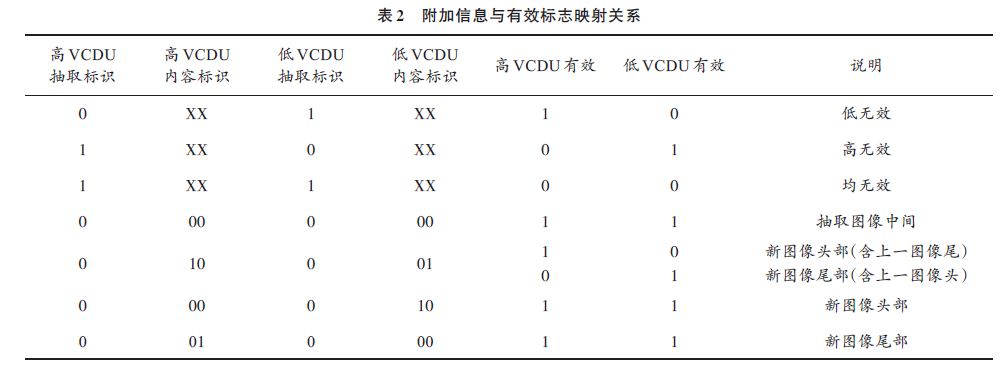

附加信息与数据一起被存到存储芯片中。在回放时,读取附加信息,解析出高VCDU有效/无效信号和低VCDU有效/无效信号。由回放请求模块进行数据滤除,保证仅回放有效数据,并且为完整图像。

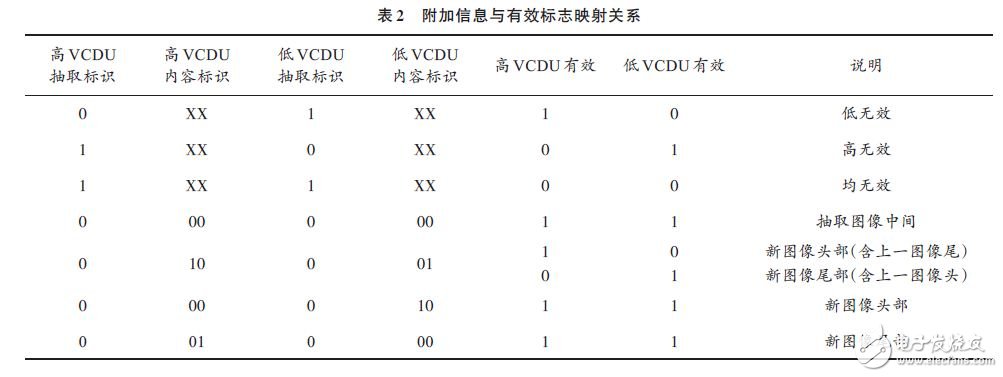

附加信息与有效标志映射关系见表2.对输入数据的各种情况,按照表2中映射关系解析出有效/无效信号。

数据过滤模块设置缓存,根据高低VCDU有效标示控制缓存地址,为1进行读取,为0跳过无效的VCDU数据,实现数据的滤除。

1.2 实时性设计

方法中必须获取到帧头VCDU 信息和帧尾VCDU信息才会更新图像数据帧地址寄存器,即在收到一整幅图像之后才能进行回放。

抽取的延时计算一幅图像第一比特输出和输入时间之差,最坏情况时第N 幅图像已经写入,第N + 1 幅图像尾部没有写完,即在第N 幅图像头写入后两幅图像时间才开始回放。抽取过程中延迟时间=两幅图像时间+数据回放时间。工程中,图像生成速率为10幅/s,一幅图像的生成时间按 100 ms计算。

回放数据的时间为数据从FLASH芯片中读出时间和数据缓存时间,每页2 KB,读取时间约320 μs;其余处理路径上的寄存时间《10 μs.因此,抽取过程中延迟时间约为200.33 ms ,完全可以满足图像的回放观看需要。

1.3 速率自适应设计

图像抽取的比例(即抽取图像的间隔)与输入速率和回放速率相关,在工程应用中,输入图像速率为 13.33 Mb/s,回放速率为50 Kb/s,其中图像有效数据率为41.808 Kb/s,一幅图像大小为131 080 B,每幅图像形成149个VCDU帧,下行共149×1 024 B=152 576 B.

以50 Kb/s 速率进行回放,回放一幅图像需要152 576×8/41 808=29.19 s,此过程中记录图像29.19×10=291.9,约292帧,即间隔约292帧抽取一幅图像。

实现速率自适应的关键是抽取方法的各个环节和输入速率、回放速率均没有耦合。

输入数据通过帧头尾识别,划分为标识出头尾的VCDU,输入数据速率改变,仅影响VCDU 的数据间隔。

VCDU 的数据间隔实际影响写控制模块对FLASH 芯片 *** 作的频繁程度。因此在输入速率符合入口速率的要求时,数据可以被正常存储并产生附加信息,输入速率对方法没有影响。

回放数据从FLASH读出后,解析附加信息,进行缓存、滤除无效数据后输出回放。回放速率的改变,将导致回放控制模块加载头尾寄存器的间隔改变。回放速率减慢,加载间隔增长,头尾地址寄存器将被写控制模块刷新多次,即抽取图像的间隔自动增大。回放速率加快,加载间隔减小,由于在算法设计中考虑只有新的头尾地址被存入时,回放模块才能正确加载新地址,否则回放模块会停止在当前地址继续等待新图像。因此抽取图像的间隔会自动减小,当没有新图像时,抽取模块会等待新数据进入。

速率的自适应有利于算法的稳定性和通用性,在输入、回放速率改变时不需要改变抽取程序即可实现抽取回放功能。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)