在集成电路的设计中,电阻器不是主要的器件,却是必不可少的。如果设计不当,会对整个 电路有很大的影响,并且会使芯片的面积很大,从而增加成本。

目前,在设计中使用的主要有3种电阻器:多晶硅、MOS管以及电容电阻。在设计中,要根据需要灵活运用这3种电阻,使芯片的设计达到最优。

1、多晶硅电阻

集成电路中的单片电阻器距离理想电阻都比较远,在标准的MOS工艺中,最理想的无源电阻器是多晶硅条。一个均匀的平板电阻可以表示为:

![]()

式中:ρ为电阻率;t为薄板厚度;R□=(ρ/t)?为薄层电阻率,单位为Ω/□;L/W为长宽比。由于常用的薄层电阻很小,通常多晶硅最大的电阻率为100 Ω/□,而设计规则又确定了多晶硅条宽度的最小值,因此高值的电阻需要很大的尺寸,由于芯片面积的限制,实际上是很难实现的。当然也可以用扩散条来做薄层电阻,但是由于工艺的不稳定性,通常很容易受温度和电压的影响,很难精确控制其绝对数值。寄生效果也十分明显。

无论多晶硅还是扩散层,他们的电阻的变化范围都很大,与注入材料中的杂质浓度有关。不 容易计算准确值。由于上述原因,在集成电路中经常使用有源电阻器。

2、MOS管电阻

MOS管为三端器件,适当连接这三个端,MOS管就变成两端的有源电阻。这种电阻器主要原理 是利用晶体管在一定偏置下的等效电阻。可以代替多晶硅或扩散电阻,以提供直流电压降,或在小范围内呈线性的小信号交流电阻。在大多数的情况下,获得小信号电阻所需要的面积比直线性重要得多。一个MOS器件就是一个模拟电阻,与等价的多晶硅或跨三电阻相比,其尺寸要小得多。

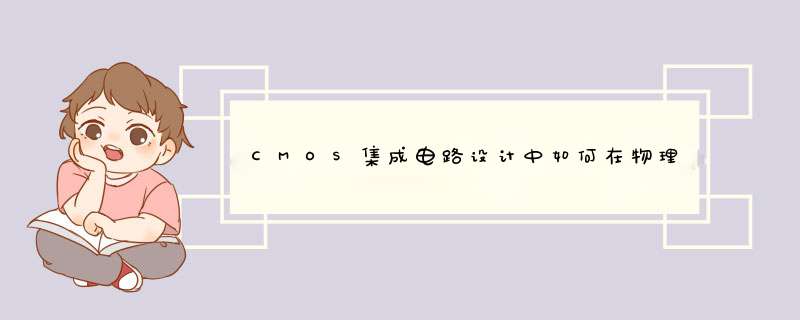

简单地把n沟道或p沟道增强性MOS管的栅极接到漏极上就得到了类似MOS晶体管的有源电阻。对于n沟道器件,应该尽可能地把源极接到最负的电源电压上,这样可以消除衬底的影响。同样p沟道器件源极应该接到最正的电源电压上。此时,VGS=VDS,如图1(a),(b)所示。

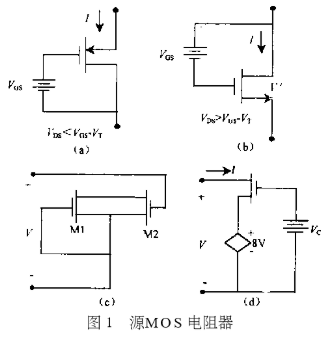

图1(a)的MOS晶体管偏置在线性区工作,图2所示为有源电阻跨导曲线ID-VG S的大信号特性。这一曲线对n沟道、p沟道增强型器件都适用。可以看出,电阻为非线性的。但是在实际中,由于信号摆动的幅度很小,所以实际上这种电阻可以很好地工作。根据公式

![]()

其中:K′=μ0C0X。可以看出,如果VDS《(VGS-VT),则ID与VDS之间关系为直线性(假定VGS与VDS无关,由此产生一个等效电阻R=KL/W,K=1/[μ0C0X(VGS-VT)],μ0为载流子的表面迁移率,C0X为栅沟电容密度;K值通常在1 000~3 00 0Ω/□。实验证明,在VDS《0.5(VGS-V T)时,近似情况是十分良好的。

图1(c),(d)虽然可以改进电阻率的线性,但是牺牲了面积增加了复杂度。

用有源电阻得到大的直流电压需要大的电流,或者远小于1的W/L比值。可以采用级连的方法克服这一问题即将每一级的G,D与上一级的S相连。这样可以使W/L接近于1且使用较小的直流电流。

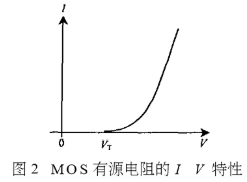

在设计中有时要用到交流电阻,这时其直流电流应为零。图1所示的有源电阻不能满足此条 件,因为这时要求其阻值为无穷大。显然这是不可能的。这时可以利用MOS管的开关特性来实现,如图3(a)所示。MOS开关的特性近似为直线,没有直流失调。这时通过控制栅源之间的电压值就可以得到ΔV为1 V的线性交流电阻。

为了尽可能夸大线性区并抵消体效应,电阻往往以差动方式成对出现,如图3(b)所示的一 对差动结构的交流电阻。注意,加到电阻器左边的是差动信号(V1);右边则处于相同电位。

3、电容电阻

交流电阻还可以采用开关和电容器来实现。经验表明,如果时钟频率足够高,开关和电容的组合就可以当作电阻来使用。其阻值取决于时钟频率和电容值。

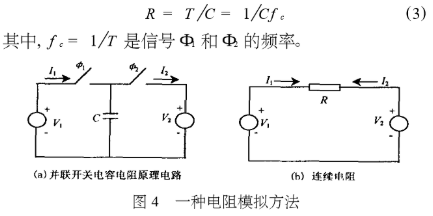

图4是一种电阻模拟方法,称为“并联开关电容结构”。在特定的条件下,按照采样系统理论,可以近似为图4(b)所示的电阻。其中V1和V2为两个独立的直流电压源,其按照足够高的速率采样,在周期内的变化可忽略不计。通过计算可得:

其中,fc=1/T是信号Φ1和Φ2的频率。

这种方法可以在面积很小的硅片上得到很大的电阻。例如,设电容器为多晶硅多晶硅型,时钟频率100 kHz,要求实现1 MΩ的电阻,求其面积。根据式(3)可知电容为10 pF。假设单位面积的电容为0.2 pF/mil2,则面积为50 mil2。如果用多晶硅,取最大可能值100 Ω,并取其最小宽度,那么需要900 mil2。当然在开关电容电阻中除了电容面积外还需要两个面积极小的MOS管做开关。可以看出,电容电阻比多晶硅电阻的面积少了很多。而在集成电路设计中这是十分重要的,虽然增加了2个MOS管,但与所减少的面积相比是可忽略的。实际上所节省的面积远不止此,因为多晶硅条的电阻率很难达到100 Ω/□。当然,利用电容实现电阻还有其他的方法,在此不再赘述。

4、结语

本文集中讨论了怎样在物理层上实现电阻。实际上,MOS工艺在这方面提供了不少方便。这些电阻器可以与其他的元器件一起使用。使用开关和电容模拟电阻,可以减轻漏极电流受漏—源电压的影响。对于电容电阻器,由于其电阻值与电容大小成反比,因此有效的RC时间常数就与电容之比成正比,从而可以用电容和开关电容电阻准确的实现电路中要求的时间常数;而使用有源器件的电阻,可以使电阻尺寸最小。多晶硅电阻则是最简单的。在设计中要灵活运用这三种不同的方式。

责任编辑:gt

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)