串行闪存简介

在数字电视、高端打印机、个人电脑、数码相机及机顶盒等消费类电子产品领域,愈演愈烈的竞争迫使制造商要求设计工程师在降低系统成本方面竭尽全力,同时不能以牺牲性能为代价。 为此,许多内存制造商尝试缩小芯片尺寸、尽可能减少功能集并通过地址与数据引脚复用减少引脚数目。 但面对降低存储器子系统成本并保持系统性能方面日益严峻的需求,上述方法无法从根本解决问题。 第一代串行外围接口(SPI)设备虽成功降低了成本,但只能满足小容量和低性能之需。 例如,相比并行NOR,读取性能降低了将近80%。 高端电子系统设计人员需要更多存储器和尽可能最佳的性能表现,这是他们设计的竞争力与创新性之源。 面对这样的挑战,制造商必须放眼整个系统而非局限于单独的组件。 一种新型闪存接口应运而生。

最初SPI接口的出现使设计简化并且降低了成本,同时充分满足低端应用所需性能。 SPI设备通常以串行方式读取信息,或者一次读取一位,所需连接较少,因而只要更少的引脚。

多I/O SPI提升系统性能

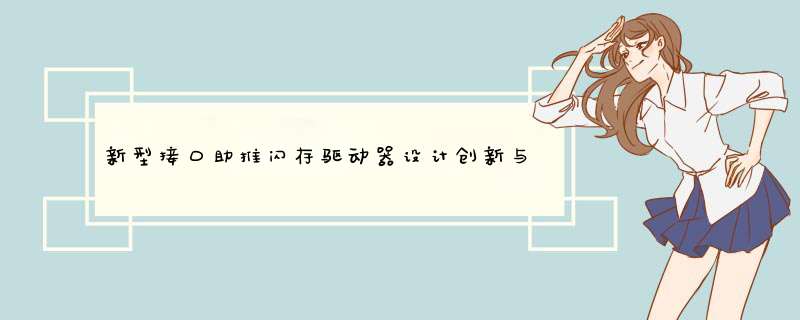

不过单I/O (SIO) SPI才仅仅是开始。 多I/O SPI将性能提升到新的水平。 多I/O (MIO) SPI设备在未改变SPI设备和封装大小及引脚数的前提下即可支持更高带宽。 通过多I/O,设备可以同时收发一位、二位或四位的数据,实现速度的飞跃,但对总引脚(八个)或活动引脚(五个)的要求并未改变,延续了SIO SPI的独有优势。 性能的提升意味着串行设备可用以支持更快的XIP代码执行,隐性缩减系统所需RAM容量并使系统启动时间有所缩短。

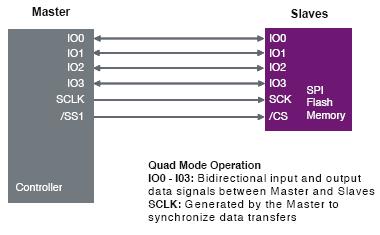

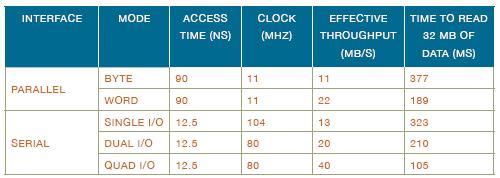

与标准串行闪存设备相比,双I/O(2位数据总线)接口支持双倍传输速率,而四I/O(4位数据总线)接口可将吞吐量提升至原来的四倍,能够适应性能要求更高、范围更广泛的应用场合。

SPI闪存在单I/O模式下以高达104兆赫(MHz)的时钟率支持越来越高的性能。 在4位模式运行中使用MIO SPI设备时,80 MHz相当于在320 MHz的有效时钟频率下以高达40MB/s的连续传输速率运行闪存。 这是以50 MHz时钟率运行的标准串行闪存传输速率的6倍多。 此外,与单I/O模式相比,它可减少每个读取指令所需的时钟数(从40减少到12),从而将随机存取开销降低70%以上。

为处理日益庞大的数据,四I/O SPI可实现更快的启动时间。 以四I/O模式运行的128M MIO SPI(串行时钟80MHz)的启动速度是标准128M SIO SPI(串行时钟104MHz)的3倍。 相比标准并行NOR(初始存取时间90ns),以四I/O模式运行的128M MIO SPI(串行时钟80MHz)在启动时要快差不多4倍。

选择恰当的存储器子系统

WebFeet(2009年10月)数据显示,在过去的二十年间,NOR闪存成长为一个价值50亿美元的巨大市场。 当前生产的NOR闪存有百分之九十采用并行NOR接口。 NOR闪存的优势包括快速随机存取和高可靠性。 快速随机存取最适用于横向寻址架构,在其中主机呈现字节或字级随机地址,数据传输到I/O需要约100ns。

在过去的几十年里,并行NOR模式的内存子系统结构使用主机ASIC以实现芯片内执行(XIP),从而加速启动和存储器控制器配置,在某些情况下,将代码映射到DRAM实现 *** 作系统代码执行。

并行NOR接口之所以广泛应用出自以下几个原因。 并行NOR闪存拥有强大的供应商体系,ASIC设计人员和软件架构设计人员也不想使以前的投入付诸东流,这意味着在多年内并行NOR闪存不会退出市场。

但是,目前许多应用及市场

需要新的存储器解决方案。 对于这些应用,多IO SPI是个极具竞争力的替代方案。 业内已对此投入大量努力以改善接口来满足更高性能的应用需求。 主机设计人员对其内存子系统需求进行评估,发现SPI可实现快速初始存取与高性能脉冲串式模式间的平衡。

虽然并行NOR闪存具有横向寻址功能以实现快速初始存取,不过SPI采用了内部多组架构,这是无缝连续脉冲串应用的理想选择,其中的代码或数据可快速传输至DRAM用于主机控制器存取。 系统设计人员现在可以根据其存储器子系统架构所需在并行和串行接口间加以选择。

对于SPI解决方案的适合应用,从并行闪存到SPI的切换并不只是作用于闪存。 由SPI带来的若干系统级优势如下:

1) 简化了ASIC存储器控制器设计,从而降低工程成本并缩短产品上市时间。

2) 通过减少约50个引脚降低了ASIC成本,同时保留将来扩展到更高容量的可扩展性。

3) 通过减少互连降低了印刷电路板(PCB)成本,且小型SOIC8封装占用更少电路板空间。 在某些情况下,系统设计人员可将六层PCB板简化为双层板。

除了上述系统方面的优势,SPI闪存组件成本也得到降低:

1) 因减少约50个焊盘使得芯片尺寸缩小,此外简化了SPI芯片上的外围逻辑。

2) 通过减少约80%引脚数和封装材料降低了封装成本。

SPI另一关键优势在于,容量的可扩展性并不会增加引脚数。 并行闪存容量每提升一级就需增加一个地址引脚。 通过SPI的数据和I/O结构复用功能,系统设计人员可将其用于更高容量的设备,无需专门增加ASIC地址引脚。

例如,不同于并行NOR闪存,从32Mb向64Mb或128Mb迁移SPI设计无需额外的地址引脚。 这使得客户电路板设计的容量迁移更为便捷,并能够向应用程序代码加入更多功能。

设计周期推动SPI应用

使用多I/O SPI可以更轻松地构建新功能,突显独创与创新。 通过减少引脚数,系统设计人员不断寻求新的方式来利用高性能SPI设备进行创新并使系统应用价值得到提升。

快速设计周期和不断降低系统成本是消费类产品领域的热点。 是否选用创新的存储器子系统,地区因素占很大比重。 中国的OEM和ODM厂商会在原型设计中装配许多消费类系统级芯片(SoC)设计成品(如数字电视ASIC),产品则销往本地和出口市场。 为满足消费类产品市场对最高性价比的需求,上述地区的设计人员已接受并采纳了SPI。

消费类产品领域中的应用得益于SPI的例子有许多:

1) 替代并行NOR接口后只需更少的ASIC引脚,数字电视设计人员使用节约下来的引脚另外增加了一个HDMI端口。

2) 多功能打印机利用1个8针SOIC封装的SPI接口,降低了印刷电路板的成本。

3) 机顶盒的应用从大部分XIP模式迁移到引导XIP 和DRAM请求页面调度模式。

4) 数码相机降低了ASIC封装成本低并减少了引脚,同时缩小了PCB和存储器子系统。

除了基于架构的考虑,许多ASIC设计人员的选择单纯为降低ASIC成本,将SPI引脚减少带来的节约优势传递给最终用户。

SPI接口发展前景

设计人员总是不想使以前的投入付诸东流。 未来SPI存储器总线的推广将提升性能以满足新的应用需求,同时提供向下兼容模式,以确保无缝迁移到创新的SPI存储器子系统。

本文是对多I/O SPI闪存缘何能够提升性能以及降低成本的一些见解。 设计工程师应关注新型闪存接口并探索其他提升系统性能、减少引脚数量以及降低整体系统成本的可能方案。

Kevin Widmer是Spansion的战略营销总监。 Widmer拥有20年的业内资深经验,他最近就任Spansion 和 Micron Technology在无线和嵌入式应用全球技术与战略营销方面的总监和高管职位。 他曾获得18项关于半导体存储器架构方面的美国专利。Widmer拥有工商管理硕士学位,以及佛罗里达大西洋大学的电子工程和物理学理学学士学位。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)