功耗效率真是一个“热点”话题,请原谅我抖机灵。现在,代工厂和半导体制造商都对如何降低功耗充满了热情,就像之前他们趋之若鹜地为提高时钟频率和性能一样努力。AMD自然也是这一潮流中的一员。在该公司近日发表的白皮书中,该公司提到了其25×20项目,该项目的目标是在五年内将每瓦特功耗的性能水平提升25倍。

如果你对微处理器和发展趋势和一般的功耗方面的创新都一直有保持关注,这份白皮书的内容可能对你来说并不算陌生。这份白皮书介绍了HUMA(异构统一存储器存取)和异构系统架构(HSA)的优点,以及工厂工艺在能效提升上的成果。其中AMD给出的最有趣的额外信息是关于自适应电压与频率调节(AVFS)的部分。这其中最大的改进主要在Carrizo方面,但Carrizo-L平台却没有采用它们。

AVFS vs DVFS在微处理器中节省电力的方法主要有两种,一是前面提到的AVFS(自适应电压与频率调节)和DVFS(动态电压和频率调节)。英特尔和AMD已经在DVFS的道路上走过了十几年。DVFS使用的是被称为开环调节的机制。在这种类型的系统中,CPU供应商将会为不同的目标应用和使用频率决定最佳电压。DVFS并不针对任何特定的芯片进行校准;相反,英特尔和AMD等供应商通过已经验证过的静态模型来确定芯片在给定的频率下运行的工作电压。

DVFS的设计之初就给出了过量的预留。CPU的运行温度将会影响到其电压的需求。而因为AMD和英特尔并不知道其给出的SoC会在40摄氏度还是80摄氏度运行,他们调整了DVFS的模型,确保芯片在工作时不会受到损害。从而在实际工作中,系统的功耗大约是实际所需要功耗的10-20%。

据AMD授权这份白皮书的Sam Naffziger称:这种过量的设计意味着大量的浪费,因为现在的CPU功耗与电压上升的平方成正比(如果考虑到漏电,则更接近三次方)。电压值提升10%,那么功耗就将有20%的提升。

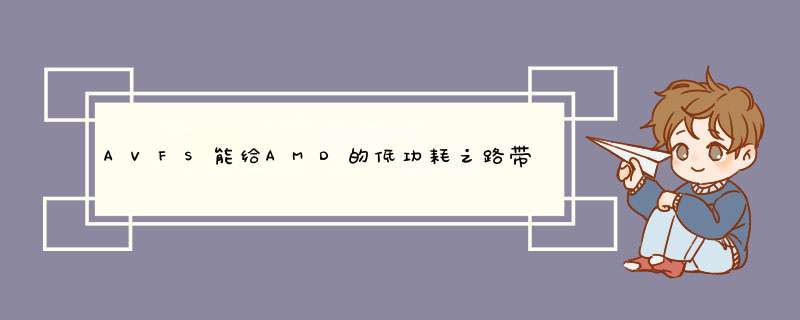

相对的,AVFS使用的则是闭环系统,在该系统中,通过芯片上的硬件机制对电压进行管理,这是通过对节温度和实时频率的实时测量得到的,然后再对电压进行调节以对其进行匹配。这种方式通过去除不要的保护性的电压范围来消除前面提到的功耗浪费。

另外AVFS还有一个优点是Naffziger没提到的,尽管目前并不清楚这和AMD的利益有无关联:AVFS可以减少工艺变化带来的影响。

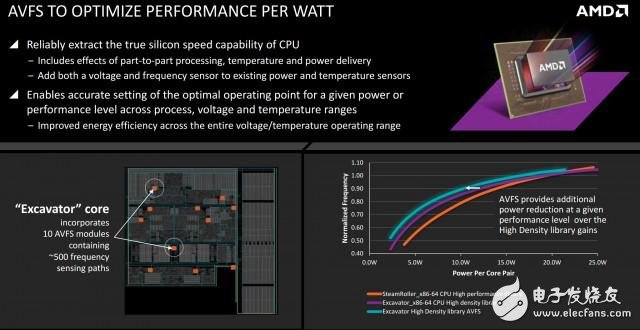

半导体制造和更进一步的产品制造的区别之一是半导体制造商并不知道其造出的芯片到底怎么样,只有测试之后才能明白。每一块晶圆都有自己独特的性质,从而导致有的芯片所需要的电压比其它芯片低,有的芯片则能达到更高的时钟频率,而有的根本就不能工作。一个建立在成熟节点上的SoC设计所面临的变化比新节点和新工艺采用时的变化更少,但变化和差异始终是存在的。

这种变化有时候直接影响了工艺的成败。

上图显示了三种不同的器件,第一种的频率是800MHz,功耗也最低,但这种芯片完全不能超频。第二种芯片的功耗更高一点,但频率上限也更高,制造商会选择使用这种芯片。而第三种的频率上限就更高了,而且达到其最大频率时所需要的电压比第二种低,但在同等频率下,它的功耗却是最高的,因为其浪费的能量也更多。在DVFS下,制造商将会将这些CPU的电压设定成1V,这是最弱的芯片需要保持稳定工作所需要的最低值。

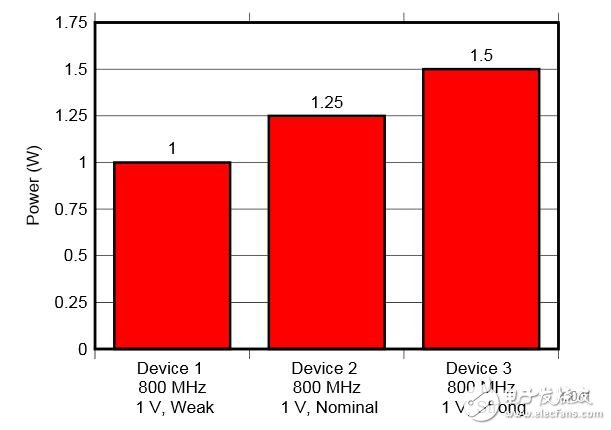

而AVFS,则提供了更多选择。通过实时测量和调整电压,AVFS可以确保芯片工作在其所需要的最佳电压值状态。如上图,只要在最弱的工作在1V就可以了,第2和第3中芯片的电压会分别调整为0.95V和0.9V。这样AVFS在能保证用户体验的同时,降低了芯片的功耗。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)