电路功能与优势

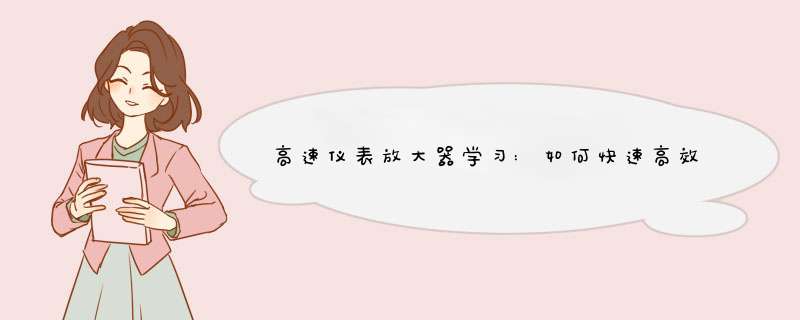

构建仪表放大器的传统方法要用3个运算放大器和7个电阻,如图1所示。这种方法需要4个精密匹配的电阻,以获得良好的共模抑制比(CMRR)。如果匹配有误差,则最终输出也会产生误差。某些节点上,一皮法或两皮法(pF)的不平衡就会导致高频CMRR显著降低,而这一情况常被忽视。

该电路采用单芯片差动放大器和激光调整薄膜电阻构成输出放大器,因此可提供良好的直流和交流精度,而且所需器件比传统方法要少。

图1. 增益G = 201的仪表放大器(原理示意图,未显示去耦和所有连接)

电路描述

该电路采用 AD8271 差动放大器和两个ADA4627-1 放大器,具有低噪声、低漂移、低失调和高速特性。对于高阻抗信号源,由于ADA4627-1的JFET输入偏置电流极低,因而是输入级放大器的理想选择。

输入级运算放大器还必须具有低失调电压和低失调电压温度漂移特性。同时需具有良好的驱动特性,以便使用低值电阻,使电阻热噪声最小。

为使本电路正常工作,必须考虑与运算放大器相关的裕量问题。

使用增益带宽积大于数MHz的运算放大器时,精心考虑布局和旁路十分重要。典型的去耦网络由一个1 μF至10 μF电解电容和一个0.01 μF至0.1 μF低电感陶瓷MLCC型电容并联构成。

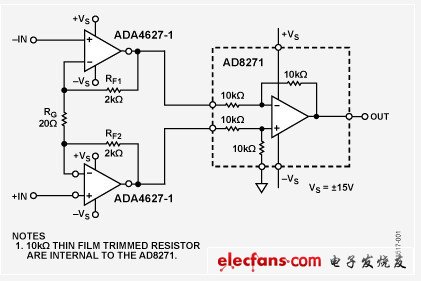

仅有低阻抗信号源时,为使噪声最低,必须保持低电压噪声。 AD8599 具有更低的噪声、失调电压漂移和电源电流,但输入偏置电流则高得多,而且所获得的带宽将比ADA4627-1低。AD8599和ADA4627-1测得的−3 dB带宽分别为56.6 kHz和87.6 kHz(参见图2)。

图2. 图1所示电路分别使用ADA4627-1和AD8599作为输入级时的带宽比较

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)