使用MCU的系统设计人员受益于摩尔定律,即通过更小封装、更低成本获得更多的丰富特性功能。嵌入式系统设计人员和MCU厂商关心数据采集系统的三个基本功能:捕获、计算和通信。理解全部功能对设计大有帮助,本文将主要关注数据采集系统的捕获阶段。

捕获

计算

信号捕获后,需要对捕获数据进行某些处理;有时仅仅需要模数转换,但是更多情况下必须要对捕获的数据样本进行计算。MCU行业中持续进行的数字化演变,带给系统开发人员更先进的信号处理水平和更高的处理器速度。因此,嵌入式开发人员现在对8位、16位和32位混合信号MCU有更多的选择余地,以便适应各种成本/性能目标。开发人员也有更多片上选择(on-chip opTIons)可用于完成系统任务。此外,MCU的硬宏(hard-macro)能自动处理,在外设中集成的功能状态机可完成常见的处理器任务。

通信

最后,为了控制过程中的信息交换,某种形式的通信是必要的。此功能可以相当简单,也可以相当复杂。通信甚至可以是模拟输出的电压或电流,通常使用数模转换器(DAC)把捕获和处理的数据转换到模拟形式来实现。

基于多功能MCU的数据采集系统

MCU数据采集系统的关键是ADC。在电子行业中最常见的ADC类型一般是逐次逼近型ADC(SAR ADC)。许多MCU使用SAR ADC是因为它在速度和性能组合上的灵活性。 在MCU中,SAR ADC的精确度可以从8位到16位,吞吐速率范围可以从极慢的按需转换请求到每秒超过100万次转换。但是ADC仅仅是完整数据采集系统中的一部分。数据采集系统的其他部分也可增加其灵活性,包括信号输入接口、参考电压接口、用于ADC的时钟和采样系统以及用于转换后ADC输出数据的数据管理。

通常情况下,模拟信号输入接口共享一个通用输入输出(I/O)缓冲器结构体,此结构体可配置为数字域或模拟域,或者也可以由两个域共用。多配置性实现方法允许设计人员根据其系统需求在多个芯片引脚上划分模拟和数字功能。作为输入多路复用器的一部分,最常见的辅助输入之一是片上的温度传感器;其他的重要输入包括内部电压。

一旦系统的输入通道配置完成,嵌入式设计人员就可以利用程序代码选择任意通道,并请求ADC转换。设计人员也可以选择免除程序代码,而允许ADC通道定序器根据预先设定的通道输入进行循环,直到检测出重要事件。

数据采集

系统的另一个重要方面是ADC参考电压(VREF)。参考电压用来设置系统的输入动态范围或量程,并能显著影响整体噪声性能。多路转换器通常用于从多种板上和外部参考电压输入中选择VREF。常用的参考电压包括MCU内部生成的缓冲带隙电压的倍频电压、片外生成的精确参考电压以及多种外部电源电压,以上可选参考电压都兼容I/O缓冲器结构体和ADC限制。

如此多的输入通道,使人们很容易想象到,在某些系统中一个或多个引脚的输入动态范围可能不兼容单一VREF电压。为了解决这个问题,Silicon Labs Precision32 MCU集成输入级联增益,根据ADC型号不同可能有0.5或1倍的增益,这样通过调整输入信号可更好的兼容选择VREF。

ADC转换循环

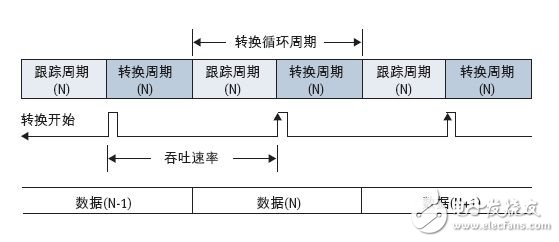

ADC的时钟系统要易于配置,以便支持MCU应用的多种用途。SAR ADC属于奈奎斯特率转换器,系统设计人员要仔细选择以满足采样率至少两倍于输入信号带宽的奈奎斯特准则。当配置ADC时,开发人员还必须考虑两个计时任务。这两个任务涉及ADC转换循环和MCU系统内的可用时钟源。转换循环有两部分组成:一个是跟踪周期,一个是转换周期,如图1所示。

图1:ADC转换循环。

跟踪周期是转换循环中当ADC输入电路连接到输入信号时所花费的那部分时间。输入采样发生在跟踪周期结束并且输入电路从输入源断开时。这一刻是由连接到ADC的数字控制信号引起的,称为转换启动(CNVST)。该命名恰如其分,CNVST标志着跟踪周期的结束和转换周期的开始。

转换周期是ADC执行逐次逼近寄存器(SAR)逻辑时的那部分ADC转换循环。ADC用于跟踪输入信号的时间量与ADC的输入负载特性、信号源的驱动能力和测量所需的精度要求相关。MCU器件规格手册列出ADC输入模型,给出ADC输入的输入电容、电阻和漏电流值。为了精确测量,开发人员应当为输入信号稳定保留足够的跟踪时间,最好超过0.5 LSB。

虽然转换周期通常是一个与SAR ADC时钟周期有关的可配置时间量,即对于每一位的判别时间,但他最好是采用CNVST请求之间的时间量描述跟踪时间,而不是SAR转换周期。简单的说,如果ADC没有处于转换状态,那他就处于跟踪状态。转换请求之间的过长时间会导致更多的跟踪时间。为了解决这个问题,Silicon Labs MCU系列产品提供在转换请求之间关闭跟踪电路的功能,从而可降低系统功耗。

ADC转换吞吐速率是转换请求的频率,通常命名为符号Fs。最大吞吐速率的设定通常由ADC的最小跟踪时间以及最小转换时间限定。恒定的吞吐速率是通过发送同样时间间隔的转换请求流来实现的。对于管理两个关键的计时任务来说,可配置的ADC时钟系统是必不可少的。

计时任务之一是生成用于转换周期期间的时钟,用于执行SAR算法。与转换周期相关的SAR时钟(SARCLK)通常来自MCU系统时钟。SARCLK的可配性需要适应MCU系统时钟,时钟频率范围从不到1MHz到超过100MHz。由于ADC内部的比较器设计,将产生SAR转换逻辑被定时的最大速率。系统设计人员必须小心配置SARCLK频率,避免超过其最大时钟速率规格。另一个计时任务是生成转换请求采样速率,其不能超过给定适当转换周期配置的ADC转换器的最大吞吐速率。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)