关键词:Verilog语言,测试台 ,行为级,以太网协议

1 引言

Verilog语言为数字系统设计人员提供了一种在广泛抽象层次上描述数字系统的方式,同时,为计算机辅助设计工具在工程设计中的应用提供了方法。该语言支持早期的行为结构设计概念,以及其后层次化结构设计的实现。在设计过程中,进行逻辑结构部分设计时可以将行为结构和层次化结构混合起来。为确认正确性可以将描述进行模拟,也提供一些用于自动设计的综合工具。Verilog语言为设计者进行大型复杂数字系统设计提供了途径。

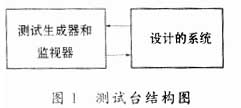

在写出 Verilog描述时,通常采用测试台的方法来组织描述。这种思想来源于工程师的工作台,把要设计的系统连接到一个测试生成器上,测试生成器在被控制的时间间隔内提供输入并监视输出。在这个模块内部还有两个模块,一个表示要设计的系统,另一个表示测试生成器和监视器,如图1所示。

2 测试系统总体结构

本系统主要是对803(10M/100Mbps以太网RTL代码)芯片设计进行测试,以完成对该芯片前端的仿真及验证工作。

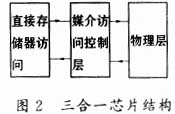

803芯片为三合一的芯片,它将物理层(PHY)、数据链路层的下层(媒介访问控制层MAC)、直接存储器访问(DMA)(包括周边器件互连总线接口(PCI Interface))三者结合在一块芯片上。其中,PHY层将数据转化为一位一位比特流的格式发送到局域网上,而MAC主要是作为数据链路层的主要模块(即底层模块),其功能在于实现CSMA/CD(802.3)协议,DMA接口部分主要用于实现网卡芯片与主机端进行数据通讯的功能。它的结构如图2所示。

对测试结构,采用两种系统仿真环境,其系统总体结构如下所述:

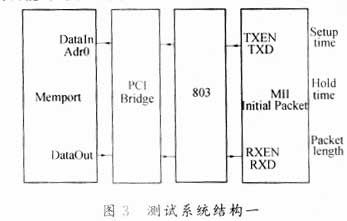

(1) 用外围的介质独立接口模块(MII) 仿真测试803 芯片所具备的以太网功能(如图3所示)。

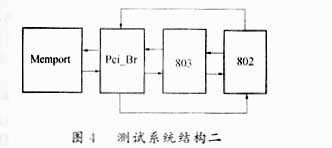

(2) 用另一个网卡IP核802_ip模块仿真803以太网芯片的功能的模型(如图4所示)。

图3和图4中的MII, Memport(存储器模块), Pci_Br(PCI桥模块)这三个模块都是用Verilog 语言描述的,即,MII是对以太网协议CSMA/CD(802.3协议)中的MII层的功能进行模拟;Pci_Br是对PCI总线桥的功能进行模拟;Memport是对主机内存进行模拟。这三个模块都是对各自模拟的功能进行行为级的描述。图中802部分是已经流片过的数字部分,但功能比803实现的功能要少。此外,803主要是为了做成三合一的片子而进行的设计,而802只是单独地作为数字部分而流片实现的。

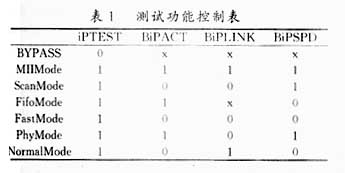

上面两种仿真测试环境的改变主要是在我们做的测试台部分进行的,针对不同的环境调用不同的环境配置文件。两种测试模式功能上的改变,主要是通过803RTL代码中引出的专门用于测试的端口输入值而实现的。即,通过改变这些端口的值进入不同的调试模式。具体如表1所示。

表1中,4个是关键测试模式:MII模式, PHY模式, FIFO模式,Normal模式。?

(1) 在MII模式下,PHY部分被忽略掉,数据包从PCI传到MII,或者从MII传到PCI,在这种模式下803芯片中的MII是用一些芯片的闲置引脚相连的;?

(2) FIFO模式的设置用于测试内部异步静态存储器的性能;?

(3) 在PHY 模式下,PHY部分应该从MAC层断开,PHY中的MII与一些存储器的闲置引脚相连。以这种方式,通过这些引脚,我们可以将数据包发送给内部的PHY,数据在PHY循环一周后从其另一端接收数据,以测试其功能;

(4) Normal 模式意味着803芯片运行在正常模式下,数据包将会从双绞线经过PHY,MAC,DMA中的异步静态存储器,最后到达PCI总线上,反方向类似。

3 系统设计思想?

为了更好地检测803芯片设计部分完成的功能是否符合CSMA/CD(带冲突检测的载波侦听多路访问)协议,可采用前面给出的两种系统结构。这两种系统结构主要包括三大模块:Memport,Pci_Br和MII。

MII模块:803芯片完成的是CSMA/CD分层协议的介质访问控制子层(MAC)的功能,它与外部的接口信号也是按照分层协议设置的。协议中的MII就是实现MAC与物理层相连的接口部分。该MII模块主要是用Verilog语言的行为级部分子集对协议中的MII和物理层进行建模,模拟协议规定的MII的功能。该模块与MAC的接口信号包括TX_ER,TXD<3:0>,TX_EN,TX_CLK,COL,RXD<3:0>,RX_EX,RX_CLK,CRS,RX_DV等标准输出输入信号,其余信号都是输入信号(Input),包括PktLength(数据包长),InitData(数据包初始数据),Pkt_Num(包序号),HoldTIme(信号保持时间),SetupTIme(信号建立时间)等控制信号。通过对这些控制信号的控制(取不同的值0或者1),在MII模块内部产生大小不同的数据包,发送给MAC层,即803芯片,然后在Pci_Br模块与803芯片的接口处检测是否收到了数据。

Pci_Br模块:按照PCI协议对PCI桥进行建模,模拟PCI桥的功能。它支持2个主设备,2个存储器端口,每个存储器端口都可以当作主设备。该模块在803芯片和存储器之间提供了一个仲裁的通道。

Memport模块:对站点的存储器的行为进行建模,存储从803芯片传来的数据,以及生成符合以太网CSMA/CD协议的数据包,并发送给803。该模块与Pci_Br模块的接口信号包括DataIn0,DataOut0,Adr0,n_RdBE0等接口信号,其余信号都是输入信号BufSize,DESNum,T1stBufPtr,R1stBufPtr等控制信号。通过对这些控制信号的控制,在Memport模块内部产生大小不同的数据包,发送给Pci_Br模块,在803芯片与MII模块的接口处检测是否收到了从Memport发送来的数据。

4 系统仿真与验证

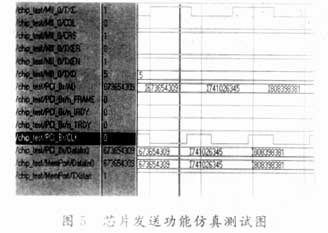

本设计在Modelsim5.4软件 *** 作平台上编译后进行时序仿真。其部分仿真波形如图5所示,图中仿真了发送过程中的一种情况。首先,在一个PCI交易周期,将存储器模块(Memport)产生的数据端口(DataIn0)的值送到Pci_Br的数据端口(DataIn0),再由Pci_Br模块根据PCI总线交易的协议,在n_FRAME,n_IRDY,n_TRDY有效的条件下,按照PCI总线的33MHz的交易时钟将数据(16'd673654309)传到AD线上,从而传到803模块中。可以看出,在网络上没有冲突(COL为0)的情况下,侦听到网络空闲时,并且在发送出错信号(TXER)和发送使能信号(TXEN)分别为0和1的条件下,按照25MHz的网络时钟频率将数据从TXD<3:0>送出。最后,通过各种发送和接收过程的仿真,完成了对803芯片的仿真与验证,确保了其功能上的有效性。

参考文献

1 Donald E T, Philip R M.硬件描述语言Verilog.刘明业, 等译.第4版.北京:清华大学出版社 ,2001

2 Jan M R. 数字集成电路设计透视.北京:清华大学出版社,1999

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)