RISC-V架构和指令集凭借其开放特性,正赢得越来越广泛的关注,无论是中国还是Intel、三星、高通等巨头都大力投入,RISC-V也被视为ARM乃至是x86的潜在“备胎”。

其实,NVIDIA对于RISC-V架构也非常关注,早早就加入了RISC-V基金会,并做了不少研究,近日还公开了在深度神经网络(DNN)中应用RISC-V指令集的可能。

NVIDIA表示,DNN需要高性能、高精度,对功耗也比较敏感,打造DNN加速并不容易,成本也很高,所以计划使用低功耗、高带宽的芯片互连技术,将多个推理加速芯片组成一个Mesh网格网络。

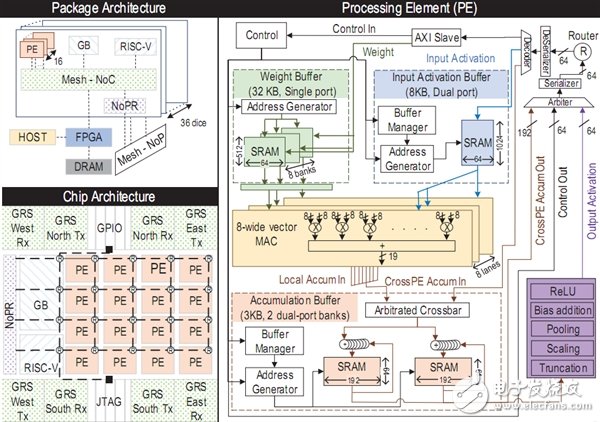

封装架构、芯片架构、PE结构

在一款研究性芯片中,NVIDIA设计了16个用于深度学习计算的处理元件(PE),搭配一个采用RISC-V指令集的控制器,可提供4.01TOPS(每秒4.01万亿次 *** 作)的算力,支持最多36块芯片互连,总算力达到128TOPS。

使用台积电16nm工艺时,单个芯片封装面积6平方毫米(2.4×2.5毫米),内核面积3.1平方毫米,36块芯片互连就是总封装面积216平方毫米、总内核面积111.6平方毫米,仍然在可控范围内,而且算下来能效可达1.15TOPS每平方毫米。

不过,NVIDIA这项研究只是一种方向性探索,暂时不会有对应的商用产品,但思路可能会融入到未来的架构和产品设计中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)