文中将要讨论的所有噪声源,设计人员可能会茫然不知所措。一种简单的做法是采取某种“推荐解决方案”;但对任何具体设计要求而言,这都是次优做法。在所有器件特性中,噪声可能是一个特别具有挑战性、难以掌握的设计课题。这些挑战常常导致一些道听途说的设计规则,并且开发中要反复试错。本文将解决相位噪声问题,目标是通过量化分析来阐明如何围绕高速数模转换器中的相位噪声贡献进行设计。本文旨在获得一种“一次成功”的设计方法,即设计不多不少,刚好满足相位噪声要求。

从一块白板开始,首先将 DAC 视作一个模块。噪声可能来自内部,因为任何实际元器件都会产生某种噪声;也可能来自外部噪声源。外部噪声源可通过 DAC 的任何外部的任何外部任意连接,包括电源、时钟和数字接口等,进入其中。图 1 显示了这些可能性。下面将对每一种可能的噪声嫌疑对象分别进行研究,以了解其重要性。

图 1.DAC 相位噪声来源

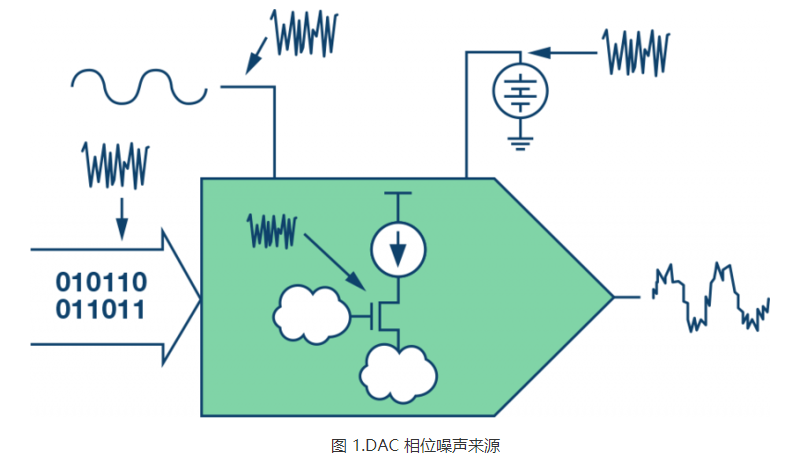

为了证明 I/O 是否需要关切,我们比较了 AD9162 系列高速 DAC 器件开启和关闭数字接口两种情况下的相位噪声。无数字接口时,器件的 NCO 模式内部生成波形,DAC 事实上变成 DDS 发生器。图 2 显示了实验结果。

图 2. 不同插值时的相位噪声

相位噪声的峰值会根据接口的具体情况发生变化。现在我们感兴趣的是,噪声和所有曲线在彼此之上。因此,对于这个产品线,尽管由于系统要求可能要注意杂散,但接口不是问题。发现接口无需担心之后,我们感兴趣的下一个方面是时钟。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)