1 引言

可测试设计(DFT)是适应集成电路的发展要求所出现的一种技术,主要任务是对电路的结构进行调整,提高电路的可测性,即可控制性和可观察性。按测试结构分,目前比较成熟的技术主要有测试点插入、内部扫描设计、内建自测试(BIST)、边界扫描设计等[1]。

内部扫描设计技术有两种:全扫描技术将电路中所有的触发器用特殊设计的具有扫描功能的触发器代替,使其在测试时链接成一个或几个移位寄存器;部分扫描技术只选择一部分触发器构成移位寄存器,降低了扫描设计的硬件消耗和测试响应时间而受到重视。在测试向量自动生成(ATPG)上,组合电路常采用D,PODEM和FAN等算法;时序电路可采用HITEC,GENTEST,CONTEST以及遗传算法等 [2]。如果被测电路(CUT)具有自己产生测试信号、自己检查输出信号的能力,则称该电路具有BIST功能。BIST主要完成测试序列生成和输出响应分析两个任务。通过分析CUT的响应输出,判断CUT是否有故障。BIST有存储器BIST(MBIST)、逻辑电路BIST(LBIST)和 DBIST[3]等几种。

2 IP核的DFT方法

在SOC中通常嵌入多个IP核,它们电路逻辑非常复杂且对时序要求非常严格,因此不同类型的IP核有不同的可测试性设计方法。

2.1 专用数字逻辑模块

数字逻辑模块的可测试性设计一般采用内部扫描设计技术,但随着芯片规模向着上千万门级发展,传统的内部扫描设计会生成数目众多的相当长的测试向量。由于测试生成和测试响应分析都在外部ATE上,扫描输入输出时间过长,导致测试成本急剧增加,故需要对传统的内部扫描设计技术做出改进。

可引入伪内建自测试(PBIST)[8] 方法来减少测试数据和缩短测试时间。对于BIST来说,故障覆盖率不高是其固有的缺点,而PBIST是希望能利用内部所产生的伪随机序列,检测到尽可能多的故障。一般电路中都会有相当部分的故障是可以用随机向量来检测的,而这部分故障如果采用PBIST方法来测试,就可以充分发挥其在测试时间、测试数据量等方面的优势。在完成这部分故障的测试后,再由外部ATE提供确定性的测试向量来满足最终的故障覆盖率需求。

可引入片上多输入鉴别寄存器(OPMISR)技术[9],对测试响应进行压缩,输出的测试结果是 MISR压缩后的数据,从而降低对ATE缓存容量的要求。利用OPMISR技术在测试模式时可把每条扫描链从中间一分为二,这样原来的一条扫描链相当于两条扫描链了,从而倍增扫描链条数,且单条扫描链上的寄存器数目是原来的一半,所以测试向量移位输入所需的时钟周期也相应减半。同时增加的MIST电路把原本在ATE上完成的信号鉴别工作部分转移到了片内进行,对测试响应进行了压缩,减小了生成的ATPG文件。

Mentor Graphics[7]的嵌入式决定性测试(EDT)技术,采用测试数据压缩技术,对测试激励和测试响应都进行压缩,通常能带来数十倍的测试数据压缩率。EDT在芯片上增加解压缩模块,利用环路发生器和相位转换电路两个逻辑块,对来自于ATE的压缩激励向量进行解压处理,产生内部扫描链上的测试激励向量。EDT同时在芯片内增加压缩模块,利用异或树和掩盖逻辑电路两个逻辑块,对内部扫描链输出的测试响应向量进行压缩处理后输出给ATE。

2.2 存储器核

存储器内建自测试是将BIST逻辑电路嵌入芯片内部,通过给相应存储器核的外围加一层测试控制电路,作为存储器核与芯片系统其他逻辑电路的接口,负责相应的测试及控制功能,最终实现片上自动测试存储器核。以SRAM为例,重要的测试算法有MATS+,MarchC-,MarchA和MarchB等[10] 。

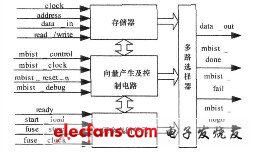

SOC芯片中片上存储器占芯片面积比重不断增大,导致了芯片成品率降低。可以采用基于电子保险丝的片上存储器修复系统技术 [11],利用冗余存储器里的冗余行和列来替代失效行或列,从而使失效存储器正常工作,来提高芯片的成品率。其结构可以与MBIST结合在一起,修复功能运行受 MBIST的控制器控制。

2.3 微处理器核

对一个上百万门的嵌入式微控制器,如采用全扫描设计可以取得较高的故障覆盖率,但它由于可能在处理器关键路径上增加可测试性电路,从而增加电路延时,降低电路性能。因此芯核的数据通路通常采用基于指令的LBIST方法来进行测试 [4,12]。

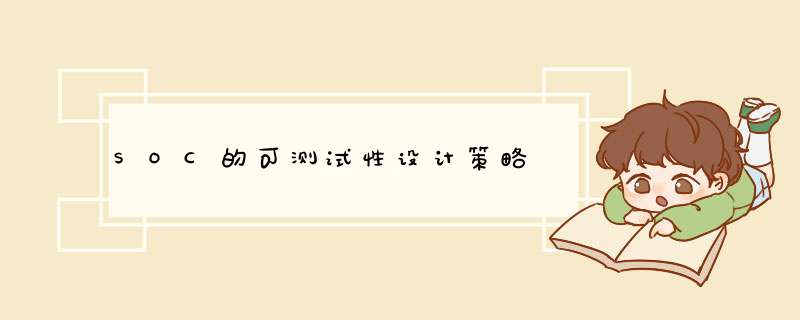

微处理器核的数据通路主要由三个部分组成:程序计数器及指令提取单元、指令译码逻辑以及微处理指令执行单元。LBIST方法需要对此增加三个寄存器:测试控制寄存器(TCR)、线性反馈移位寄存器(LFSR)以及多输入特征寄存器(MISR),如图1所示。TCR在测试模式下扫描输入微处理器的指令 *** 作码,LFSR生成随机数据,提供测试模式下的 *** 作数,而MISR压缩指令执行单元的执行结果,生成测试响应的特征值。扫描输入和扫描输出可以由边界扫描来提供。

通常微处理器核中除数据通道外还通常包含许多寄存器堆以及RAM单元,这些存储器单元通常采用MBIST方法。而芯核其他部分比如控制部分通常可以采用内部扫描设计,以获得期望的测试覆盖率。因此微处理器核测试是多种测试策略组合在一起的混合测试策略。

2.4 模拟/混合电路核

模拟电路可测试性设计的主要思想是为测试提供对选定节点的访问,可以采用以下技术提高电路的可测试性:插入测试点,如加入电流传感器来观测错误电路引起的错误电流;进行数模/模数转换,通过加入模数转换器和数模转换器,从而实现激励和响应的传播;功能结构重组,通过对电路的功能结构重组,产生区别于正常工作模式的测试模式来观测 [4]。

通过提高模拟电路的可测试性后,也可以采用 ATPG方法和BIST方法。较为典型的模拟电路ATPG方法如利用敏感性分析来产生测试向量的方法 [13],该方法可以看作是寻找一个输入测试向量,使得正确电路的响应和故障电路的响应数据上相差最大。模拟电路BIST方法通过内置测试信号发生器和特征分析器来实现,有基于振荡器的方法、基于频谱特征分析的方法和基于∑△编码的方法等 [4]。

2.5 第三方IP核

针对诸如CPU,DSP,MPEG这种通用的IP核可以采用DBIST(determinisTIc logic BIST)的测试方法[3]。这种面向IP核确定性故障模型进行芯片结构改变和测试模块加入的DBIST ,采用高效的ATPG重播种的方法进行测试向量生成。

可以利用基于扫描测试的向量生成DBIST的种子数据。DBIST结构和测试过程数据流向如图2所示。测试时,ATE通过扫描输入的方法送入以阴影寄存器(shadow register)的值来置PRPG的状态,然后PRPG产生一系列的向量(数量由步长决定),这一系列的向量逐个地通过相位转换电路进一步地扩展到更宽的位数,从而加载到CUT,其响应输出到压缩电路中,然后输入MISR产生一个鉴别码,鉴别码再被串行地送出到外界。在内部IP核测试的过程中,就同时地移入下一个种子的值到阴影寄存器中。接着继续用下一个种子来产生测试向量。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)