在ISE 中可以进行时序分析,在PlanAhead 中同样也可以进行时序分析。下面介绍用PlanAhead 进行时序分析的步骤。

一、 运行时序分析

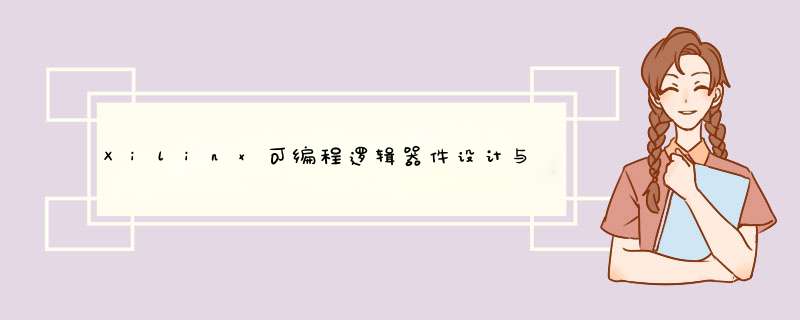

1. 在PlanAhead 中运行【File 】→ 【Open Project 】, 打开如下项目,PlanAhead_Tutorial/Projects/project_cpu_netlist/project_cpu_netlist.ppr , 会出现图10-66 所示【Floorplan】窗口。

图10-66 PlanAhead的Floorplan视图

2. 选择Floorplan – orig_results_fp选项卡。

3. 运行【Tools】→【Run TImeAhead】,打开图10-67所示对话框,设置时序分析相关属性。按图中所示设置,单击【OK】,开始时序分析。

图10-67 时序分析属性

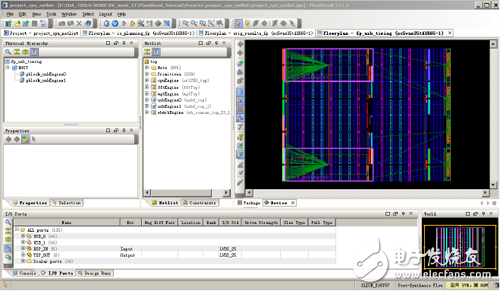

4. 分析完成,时序分析结果如图10-68所示。图中显示了时序的类型、裕量、源/目的对象、总延时、逻辑延时、网线延时百分比以及逻辑级数。

图10-68 时序分析结果【TIming Results】

图中红色为时序违例的路径,需要设计者检查并修正。

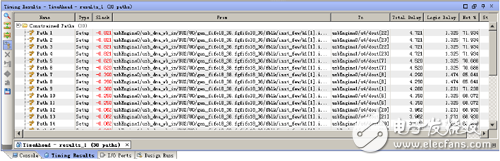

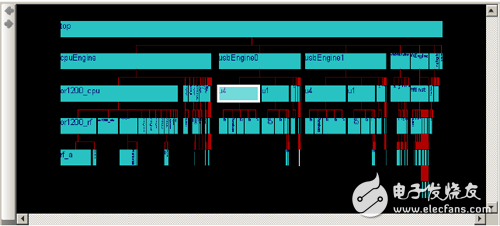

5. 选择Path1路径,并最大化【ProperTIes】窗口,如图10-69所示,可以看到此路径的详细信息,包括源时钟路径、目的时钟路径和数据路径等,其中详细列出了每条路径的组成及元件延时和网线延时信息。

图10-69 时序路径属性

二、 在【SchemaTIc】视图中探测时序路径。1. 显示原理图结构1。

在【Timing Results】窗口的Path1路径右键d出菜单中选择【Schematic】,打开如图10-70所示原理图结构视图。

2. 显示原理图结构2。

在【Timing Results】窗口的【From】列选择所有以usbEngine0/…打头的路径,单击鼠标右键,在d出菜单中选择【Schematic】,打开图10-71所示多个时序路径原理图视图。

3. 显示层次结构。

在图10-71【Schematic】窗口的右键菜单中选择【Select Primitive Parents】,再次在右键菜单中选择【Show Hierarchy】,则包含【Schematic】窗口中所示的两个部分逻辑的设计模块会显示在【Hierarchy】窗口中。如图10-72所示。

图10-70 时序路径原理图视图

图10-71 多个时序路径原理图视图

图10-72 层次视图

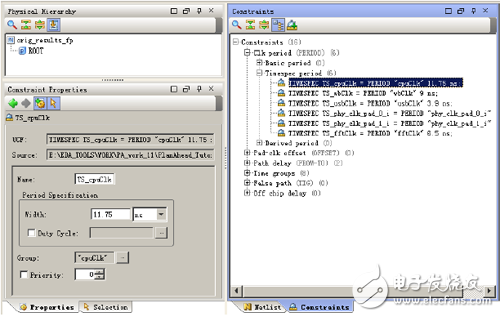

三、 编辑时序约束1. 将TS_cpuClk周期约束由11.75ns改为11.5ns。

在图10-73中,选择【Netlist】选项卡旁边的【Constraits】选项卡,选择图中所示TS_cpuClk约束,在【Constraint Properties】属性窗口可以看到此约束的相关属性,在这里可以编辑约束名、周期、占空比、分组以及优先级。这里只需将11.75ns更改为11.5ns,这时会在【Constraint Properties】属性窗口出现一个【Apply】按钮,单击就可以完成约束修改。

图10-73 修改时序约束

2. 新建时序约束。

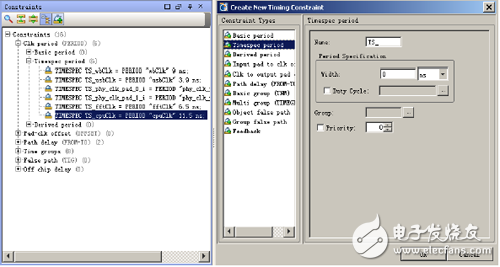

在图10-74中【Constraint】窗口单击,d出【Create New Timing Constraint】对话框,可以选择一个约束类型,并添加新的时序约束。

图10-74 新建时序约束

3. 删除时序约束。

在【Constraint】窗口选择一个时序约束,按【Del】按键,可以删除约束。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)