对于数据采集接收的一方而言,所谓源同步信号,即传输待接收的数据和时钟信号均由发送方产生。FPGA应用中,常常需要产生一些源同步接口信号传输给外设芯片,这对FPGA内部产生时钟或数据的逻辑和时序都有较严格的要求。而对于一些FPGA采集信号的应用中,常常也有时钟和数据均来自外设芯片的情况,此时对数据和时钟的采集也同样需要关注FPGA内部的逻辑和时序。当然,无论何种情况,目的只有一个,保证信号稳定可靠的被传送或接收。

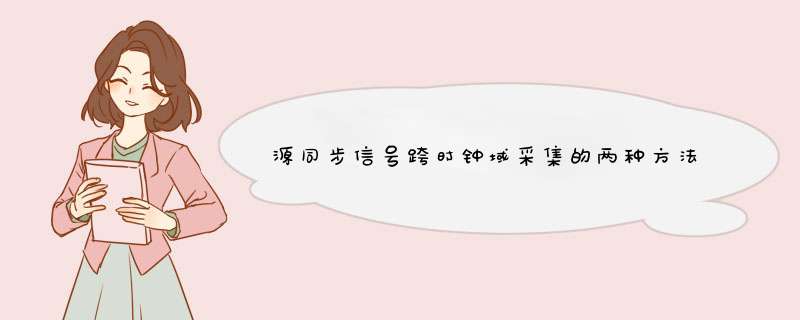

对于一个如图1所示的某视频芯片产生的源同步信号,当FPGA对其进行采集同步到另一个时钟域时,特权同学通常的做法有两种,特权同学称之为脉冲边沿检测采集法和异步FIFO采集法。下面简单的对这两种方法做一些讨论和说明。

图1

脉冲边沿检测采集法

脉冲边沿检测采集法,顾名思义,一定是应用了经典的脉冲边沿检测法来帮助或者直接采集信号。对于脉冲边沿检测法,大家可以参考特权同学的《深入浅出玩转FPGA》或者用gooogle摆渡一下。而这里尤其需要提醒大家注意的是,著名的奈奎斯特采样定理告诉我们:要从采样信号中无失真的恢复原信号,采样频率应大于两倍信号最高频率。而特权同学通过实践得出的结论与此相仿:若想稳定有效的采集到脉冲(数字信号)变化的边沿,采样频率应大于被采样脉冲最大频率的3倍。注意是要大于3倍,甚至若是可能尽量采用4倍以上的采样频率才能够达到稳定的状态。至于为什么,我想深谙此道(脉冲边沿检测法)的聪明人看完结论就已经明白了,无需特权同学再废话解释一番。

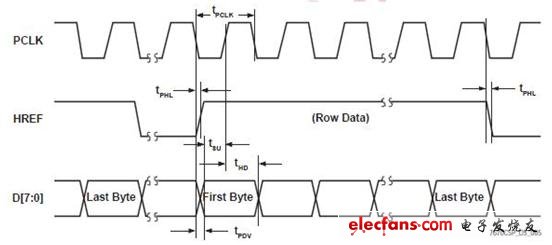

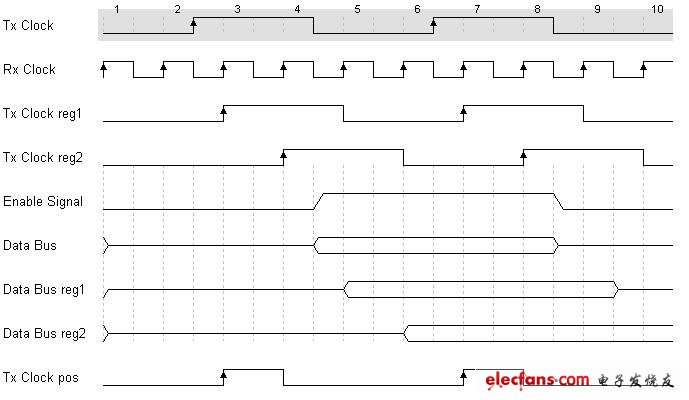

而具体的做法也很简单,把图1理想化就如图2所示。其中,待采集信号时钟Tx Clock,待采集数据使能信号Enable Signal,待采集数据总线Data Bus。FPGA内部信号采集时钟为Rx Clock,该时钟为待采集时钟的4倍。

图2

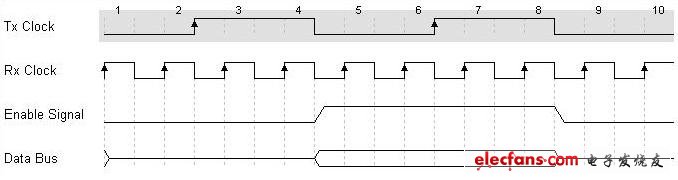

采用脉冲边沿检测法,使用Rx Clock去采集Tx Clock,Rx Clock reg1和Rx Clock reg2分别为第一级和第二级Tx Clock锁存信号。Tx Clock上升沿对应的一个有效指示信号Tx Clock pos每个Tx Clock时钟周期产生一个Rx Clock脉宽的有效高电平使能信号。从图3中可以看到,此时若用Tx Clock pos作为FPGA内部采样使能信号,虽然Tx Clock pos处于第7个Tx Clock,但是真正采集Data Bus其实已经是第8个Tx Clock上升沿了。很明显,第8个Tx Clock上升沿对准的不是Data Bus的稳定信号中央,数据很可能采集到错误值。

图3

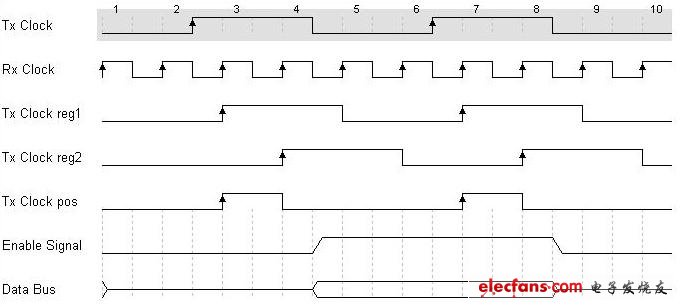

因此,通过上面的分析,还是可以采取一些变通的方式来保证第8个Tx Clock上升沿采集到Data Bus的中央值。如图4所示,采用同样的方式对Data Bus做两级信号锁存,那么第8个Tx Clock上升沿就能够在Data Bus reg2的中央采集数据了。这样做只有一点小问题,相应的需要多付出2组寄存器来锁存Data Bus。

图4

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)