简介

最高 18 位分辨率、10 MSPS 采样速率的逐次逼近型模数转换 器(ADC)可以满足许多数据采集应用的需求,包括便携式、工 业、医疗和通信应用。本文介绍如何初始化逐次逼近型 ADC 以实现有效转换。

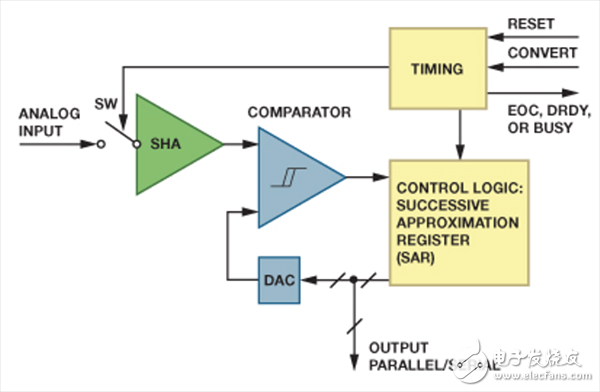

逐次逼近型架构逐次逼近型ADC由4个主要子电路构成:采样保持放大器(SHA)、 模拟比较器、参考数模转换器(DAC)和逐次逼近型寄存器(SAR)。 由于 SAR 控制着转换器的运行,因此,逐次逼近型转换器一般 称为SAR ADC。

图 1 基本 SAR ADC 架构

在上电和初始化之后,CONVERT 上的一个信号会启动转换。 开关闭合,将模拟输入连接至 SHA,后者获得输入电压。当开 关断开时,比较器将确定模拟输入(此时存储于保持电容)是 大于还是小于 DAC 电压。开始时,最高有效位(MSB)开启, 将 DAC 输出电压设为中间电平。在比较器输出建立之后,如 果 DAC 输出大于模拟输入,逐次逼近寄存器将关闭 MSB;如 果输出小于模拟输入,则会使其保持开启。下一个最高有效位 会重复这一过程,如果比较器确定 DAC 输出大于模拟输入, 则关闭 MSB;如果输出小于模拟输入,则会使其保持开启。 这个二进制搜索过程将持续下去,直到寄存器中的每一位都测 试完毕为止。结果得到的 DAC 输入是采样输入电压的数字近 似值,并由 ADC 在转换结束时输出。

与 SAR转换代码相关的因素本文将讨论与有效首次转换相关的下列因素:

* 电源顺序(AD765x-1)欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)