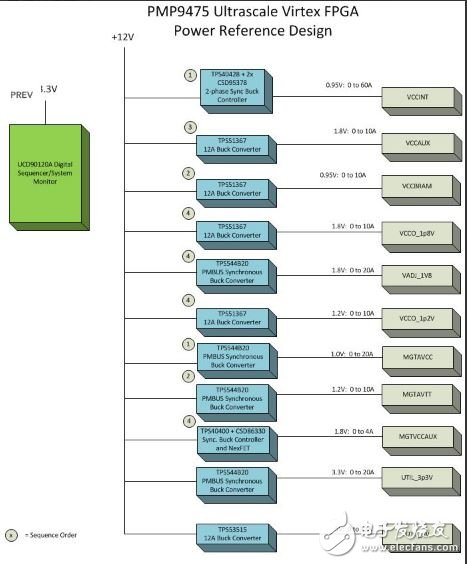

PMP9475 12V 输入参考设计以紧凑高效的设计提供为 Xilinx's Virtex? Ultrascale 系列 FPGA 供电时所需的所有电源轨。此设计使用几个 TI 的 PMBus 负载点电压稳压器以简化临界轨的设计/配置和遥测。它采用一个 UCD90120A,可实现灵活的加电和断电排序并通过 PMBus 接口实现电压监控、电流监控和电压裕量调节。

特性

提供 Xilinx Virtex Ultrascale FPGA 所需的所有电源轨

设计已经过优化,支持 12V 输入

板载加电和断电排序

具有输出电压和电流报告功能的 PMBUS 接口

电压裕量调节功能

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)