最近几年,我们已经开始看到一些有关射频(RF)CMOS工艺的参考文献和针对这些工艺的RF模型参考文献。本文将探讨这类RF所指代的真正含义,并阐述它们对RF电路设计人员的重要性。

我们可以从三个角度对RF CMOS设计进行探讨:首先,低频模拟设计人员正在将其设计提升到更高频率;其次,分立RF/微波设计人员转而借助集成手段;最后,设计人员将串行器/解串器(SERDES)这样的数字电路提升到工艺能够支持的最高频率。在上述三种情况下,RF CMOS设计都大有帮助,我们也将从这些视角出发,来解释RF CMOS本身与为其建模有何不同。

衬底

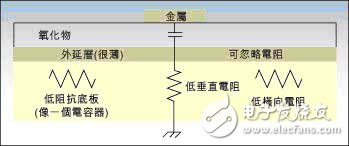

面向传统数字应用的CMOS使用已经发展到采用低电阻率的大块衬底(图1),并将器件做到一个薄的高电阻率外延层上,这样的做法往往能够同时优化闩锁(latchup)性能和良品率。

图1:基本数字CMOS模型构建在作为底基的低电阻系数大衬底上

为了保持复杂数字电路布线的灵活性,多个金属互连层在厚度上趋于一致,这使得所有金属层都具有几乎相同的布线能力。

对低频模拟/数字设计人员而言,这是一个相对理想的衬底:从(接地)衬底返回的寄生电容与我们所关注频段内的容性阻抗相比,阻抗相当小。所以,简单地提取寄生电容就能非常有效地预测实际性能。但是RF设计人员将会发现4个不尽如人意之处:a)衬底上的低阻抗实际上将寄生电容最大化了,而附着在衬底上氧化物内的金属互连所形成的导线,则最终导致相对低的特征阻抗;b)构建在衬底上的线圈与一个短路线圈(即衬底本身)紧密耦合,从而略微降低了电感值及Q值;c)到达衬底的电流,无论是容抗电流还是线圈的感应电流,都会在低阻的衬底上自由地流经很长的距离;d)试图通过并联金属层提升线圈Q值的努力收效甚微,因为如果首先使用最理想的顶层,那么其它附加层就会更加靠近衬底的短路线圈,所以并联几乎没有实质改善。

那么,与刚才描述的普遍的数字变异相比,RF CMOS工艺到底是什么呢?在许多情况下,它可以简单地被认为是使整个衬底在典型的“数字”工艺中拥有高电阻率外延层的工艺。

现在,RF设计人员却发现了一些完全不同的状况:高度绝缘的衬底实际上生成了一个与每个寄生电容串连的第二电容(因为绝缘体很厚,所以容值不大),从功能上看被相对较高的衬底阻抗分流了。

寄生电容获得了一系列额外且重要的电阻分量,具有如下一些积极效应:诸如结合区底端电容这样的大型寄生电容,在较高频率下具有近似恒定的阻抗,因为衬底阻抗反过来支配着上述容性寄生电容;线圈Q值的提高明显归功于衬底短路被削弱时产生的高阻抗,衬底电流倾向于被显著的衬底旁路阻抗约束和限制,从而使绝缘性得以提高。

针对更高线圈Q值的并联金属层带来了更好的结果,一般来说,增加较厚顶层金属层(有时采用传导性能更高的铜代替铝)的目的就是大幅提升线圈Q值。注意:用这种RF衬底构建的器件与数字工艺本质上拥有相同基本特征,在两种情况下,形成器件的最上层几个微米厚度具有相同的电阻系数。

BSIM3模型

BSIM3模型无所不在,多数CMOS设计人员都曾接触过不同版本的BSIM3模型,例如BSIM3v2或其它。将CMOS商用对其成功而言十分重要,因为该模型将基于物理和经验的参数有机地结合起来,并且很容易就可以适用于新工艺。物理分析能够预测出当物理尺度减小时会发生什么,而经验数据则允许对被制造器件的非一致单元进行有用的近似。重要的是,RF设计人员要了解在较高频率下这种重要的建模技术意味着什么,所以我们接下来会描述典型的代工厂是如何生成这样一种模型的。

模型参数的填充通常是这样完成的:即制造各种不同沟道宽度和长度的器件,然后对器件进行直流曲线记录以生成描述跨导和阻抗的参数。之后,再进行低频电容测量以填入容性参数。典型情况下,将采用类似Hspice OpTImizer的优化器对模型参数进行优化,以便在实际数据和模型数据之间得到最佳匹配。当在器件整个可能的尺度范围内,最终得到的数据没能与预期值吻合得恰到好处,那么建模者可能会对模型进行临时性存储(bin),例如,使模型按照器件的各种尺度进行分支以形成多模参数集,每个参数集在其对应的较小器件尺度范围进行优化。这就使BSIM3成为一种“紧凑模型”,能够很好地适应执行速度很快的模拟器,还可以在版图中与P核(可调整尺寸参数的物理版图单元)一起使用,从而赋予设计师极大的灵活性。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)