如今,FPGA 功能强大且管脚数目极大,可为工程师提供大量机会来提升特性和功能,同时还能降低产品成本。随着复杂度增加,将这些器件集成到印刷电路板也成为了一项严峻的挑战。数百个逻辑信号需映射到器件的物理管脚输出,同时还需保持设计的电气完整性。FPGA 复杂度增加也需要高级合成技术,如此才能更快达到时序收敛,最大程度地减少设计变更的影响以及解决特定应用要求。

直观的逻辑合成环境包括先进的优化技术、屡获殊荣的时序分析和先进的推论技术,适用于与供应商无关的设计中,可加快产品上市时间、消除设计缺陷以及提供极佳的结果质量 (QoR)。

FPGA I/O 可优化管脚分配,从而提高布通率和信号完整性。

主要优势:

■ 通过采用并行流程缩短总设计时间

■ 通过消除 PCB 信号层降低 PCB制造成本

■ 消除由于 PCB 上的过期 FPGA符号所导致的 PCB 重新设计

■ 采用高速性能优化

■ 消除与创建和维护用于 PCB 原理图的 FPGA 符号相关的成本

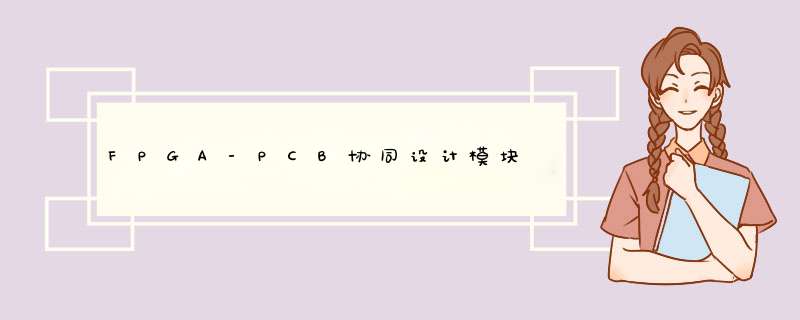

FPGA I/O OpTImizaTIon

流程集成

I/O 优化与 PADS Professional 设计流程紧密集成,在项目的任何阶段均可访问。原理图、PCB Layout 和FPGA 数据库始终保持同步,以便用户控制项目的设计数据流。另外,原理图用户可决定何时将 FPGA 数据(新数据或更新数据)传输到 PCB 设计。

在 PCB 布局或布线开始前,I/O 优化可使用 PADS 项目数据进行叠层规划以及优化初始分配。用户可将结果导出到 Layout,并在项目级别或企业库级别管理 FPGA 元件。

信号和管脚分配

要手动将数百个 HDL 信号分配到 FPGA 管脚,同时仍严格遵守 FPGA 供应商规则,这一过程难度可能很大。为简化这一流程,PADS Professional 提供简单易用的功能,以便进行自动分配、信号标准监督、简单拖放分配、支持 *** 作对象集以及动态筛选。总之,其可简化信号管脚分配 *** 作流程。每次管脚分配更改均通过 FPGA-PCB 流程管理,无论更改了哪些地方,均可保持一致。

自动化元件和符号生成

由于 FPGA 器件自身的性质,因此需要不同的符号生成流程方法。在项目生命周期内,FPGA 逻辑通常要更改数次,而符号必须与这些更改保持一致。该高级 PADS 模块功能强大,不仅可让您轻松、快捷且无误地创建符号,而且仍可完全控制符号创建流程。相比于手动符号创建,时间从数小时或数天降到了数分钟。

叠层规划

PCB 设计流程的一个重要阶段是元器件布局及其在PCB 布局上的方向。您可在 PCB Layout 流程开始前或流程中进行叠层规划。如此一来,工程师和设计人员就具有明显优势,可在项目的最初阶段进行FPGA 管脚分配更改、优化元器件布局和方向、缩短飞线以及减少飞线交互。

FPGA 多实例和优化

大多数情况下,同一个 FPGA 器件在不同项目甚至一个项目中都具有不同的逻辑功能。在项目开发期间,PADS Professional I/O 优化可自动支持这些情况。物料清单报告中列出了不同功能符号表示的FPGA 以及供应商元件编号。基本上无法成功手动执行两个或多个 FPGA 器件之间的连接优化。不过使用这个高级 PADS Professional 模块,优化算法即可评估所有可能的连接组合,从而获得最佳互连。此外,还可以最大程度地减少初始分配中产生的网络交互,提高布线完成率。

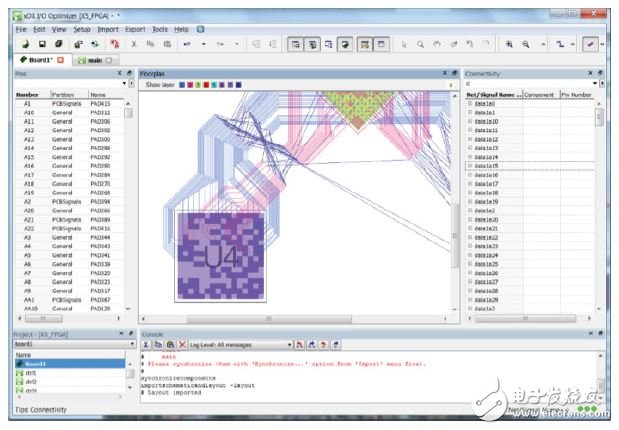

FPGA Synthesis

高级优化算法

一套独特的优化算法可自动将特定优化集中在最有可能妨碍整体性能的设计领域,例如有限状态机(FSM)、跨层次结构路径以及具有过高组合逻辑的路径。这些算法可提供自动化的启发式方法,从而交付更小更快的设计,而无需迭代人工介入。

RTL 和技术原理图查看器

编译设计时,可使用通用门进行创建并以 RTL 原理图形式查看。合成后,使用反映该数据库的技术原理图创建技术映射数据库。原理图查看器可协助您了解如何解读 RTL 并将其映射到目标 FPGA 技术中。

供应商不相关性

与供应商无关的合成可支持 Altera、LatTIce、Microsemi和 Xilinx 的器件。因此,您可使用相同的 HDL 设计源文件和约束将任意器件作为目标对象并获取合成网表,将其通过适当的供应商工具用于布局布线。此供应商不相关性使用户可以轻松将任意 FPGA 器件重新作为目标对象并分析结果,从而找到最适合您设计的 FPGA 器件。

在与供应商无关的环境中使用高级合成技术,针对每种 FPGA 器件实现特定的架构优化。

支持所有器件

除支持四大 FPGA 供应商的 FPGA 器件外,PADS FPGA-PCB 协同设计模块还全面支持 Altera Quartus II、LatTIce Diamond 和 ispLEVER、Microsemi Libero 和Designer 以及 Xilinx ISE 和 Vivado 等 FPGA 供应商工具。

简化约束流程

为适应当今高度复杂的 FPGA 设计流程,需要支持各种约束源,包括 HDL 代码、SDC 文件和工具中的全局约束集等特定约束源。请务必指定时钟频率、输入/输出延迟和时序异常(如:合成中的多循环和伪路径)等共同时序约束,以此确保从合成中获取最佳结果。

门控时钟转换

ASIC 设计人员通常使用门控时钟进行功率管理和其他 *** 作。但映射到 FPGA 时,这些门控时钟会导致较大的时钟偏移、创建假信号以及阻碍时序分析。门控时钟使用FPGA 中适当的启用信号自动进行转换。

DSP 和 RAM 推论优化

当今的高级 FPGA 器件除常规逻辑模块外还包含 DSP 和 RAM嵌入式模块。这样一来,合成工具可了解各种 RTL 编码样式,将其映射到适当的 DSP或 RAM 模块,从而充分利用资源并获得最佳性能。PADS Professional FPGA-PCB 协同设计模块具有先进的推论和优化功能,可以最大限度地利用嵌入式资源,从而提高面积利用率和频率。

Verilog、SystemVerilog 和 VHDL 支持

通过使用 Verilog、SystemVerilog 和 VHDL/VHDL-2008等业内领先语言支持,设计人员可采用这些格式的任意组合创建和合成 RTL 设计,从而获得最佳结果。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)