HIL仿真是一种功能强大的测试方法,可以用于更加有效的测试嵌入式控制系统。当测试嵌入式控制系统时,从安全性,可行性和合理的成本上考虑,使用全系统进行所有必要的测试是不现实的。您可以使用HIL仿真来模拟部分系统以面对这些挑战,在将整个系统进行实际测试之前使您能够在虚拟环境下测试嵌入式控制器件。有了这个功能,即使您要测试的系统变得更加复杂,您也可以以一种具有成本效益的方式维持可靠性和市场投放。要更多地了解HIL测试如何改善控制系统验证,请观看什么是HIL测试网上视频. 本教程讨论了各种HIL测试系统架构和如何去实现它们。

1. HIL测试系统的组成

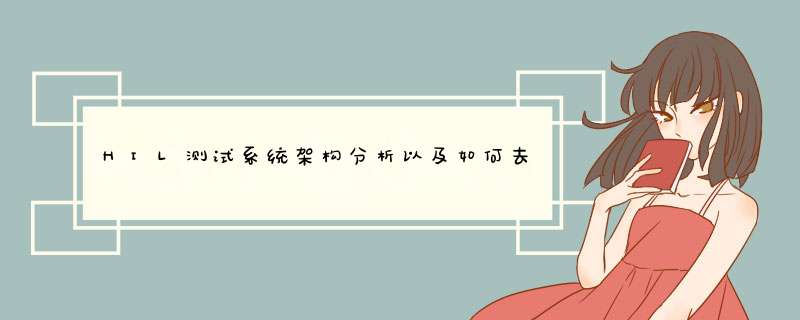

图1. 一个HIL测试系统由三个主要部分组成:一个 *** 作界面,一个实时处理器和I/O接口。

2. 硬件故障插入

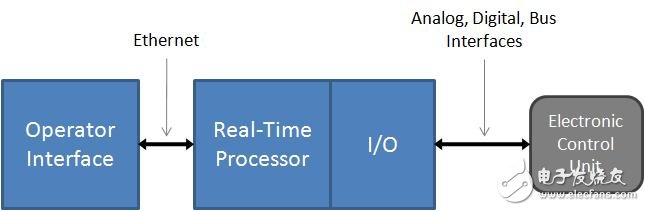

许多HIL测试系统使用硬件故障插入在ECU和其余要测试的系统之间产生信号故障,来测试,描述和验证在这些情况下的器件性能。要做到这一点,您可以在I/O接口和ECU之间插入故障插入单元(FIUs),从而允许HIL测试系统在正常运行和诸如对地短路或开路之类的故障状态之间切换接口信号。

图2. 您可以使用硬件故障插入来测试信号故障期间ECU的性能

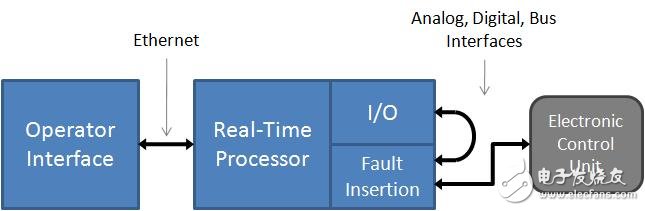

3. 测试多ECU系统一些嵌入式控制系统,例如汽车,飞机或者风力发电站,使用一起联网工作的多ECU协同运行。尽管每一个ECU最初被独立测试过,然而系统一体化HIL测试系统,如整车模拟器或铁鸟模拟器,还是经常被采用以提供更完整的虚拟测试。

图3. 汽车,飞机和风力发电站使用多ECU

当测试一个多ECU控制系统时(甚至一些单ECU控制系统),经常出现两个需求:附加处理能力和简化连线。

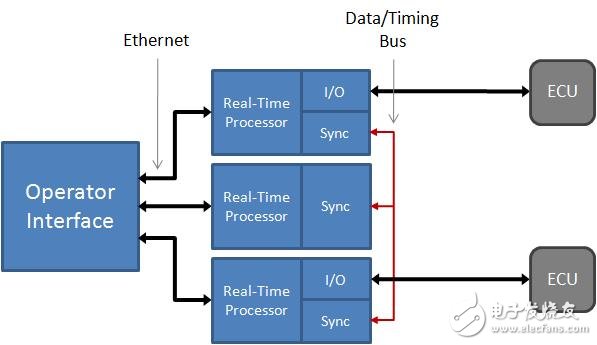

4. 额外的处理能力-分布式处理即使采用最新的多核处理能力,一些系统仍要求更多的,超过单底板的处理能力。为应对这种挑战,您可以使用分布式处理技术来满足这些系统的执行要求。在高通道数的系统中,其需求超出了简单的增加处理能力,额外的I/O也是必不可少的。相比之下,采用大规模,耗费处理器设计的系统经常使用附加的底板,仅仅是为了提供额外的处理能力,从而允许那些处理器能以很高的效率应用于单个任务。根据仿真任务的分布情况,可能需要在底板之间共享触发和定时信号,并提供确定的数据镜像来提高协同运作的能力。

图4.当为得到附加处理能力采用多重底板时,在它们之间提供时间和数据同步接口是很有必要的。

5. 简化连线-分布式I/O实现和维护高通道数系统的连线会面对昂贵和费时的挑战。这些系统需要在ECU和HIL测试系统之间连接成百上千个信号,经常为补偿空间要求跨越很多米。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)