基于赛灵思 ZC706 评估套件的平台被证实用作高通的 MRAM 测试,足够快速灵活。

电子产业正在大力投资开发PRAM、MRAM和RRAM等新型存储器技术。新型存储器技术测试芯片的性能快速提高,但这种存储器要做到能与传统存储器全面抗衡乃至取代传统存储器还需要更多的努力。

通常说来,有了新型存储器技术的测试芯片,能够完成制造相关的基础测试,例如会检查固化故障、转换故障和地址解码故障等。同时还有一种测试也是必需的,那就是要进行性能相关的测试,了解芯片可靠存取的速度能有多快,以及芯片存取速度如何影响整个计算系统性能。

为了成功进行规划的性能测试,测试环境必须能够生成可配置的数字波形来存取芯片。同时还要创建整个计算环境来测量芯片存取速度的影响。创建或购买测试环境、满足上述需求有多种方法。我们在高通的团队决定采用赛灵思 Zynq®-7000 All Programmable SoC ZC706 评估套件来打造自己的环境。

存储器进出

DRAM、SRAM 和闪存等传统存储器技术用存储器单元中的电荷来存储 0 和 1。DRAM 广泛被 PC和移动计算设备用来运行程序和存储临时数据。SRAM 通常用作微处理器的高速缓存存储器和寄存器薄,同时也经常用于对功耗问题很敏感的嵌入式系统中。与 DRAM 和 SRAM 不同,闪存存储器在系统断电后仍能永久保存数据。闪存存储器的运行速度比其他存储器要慢,大量编程循环后可能会磨损。

相对于传统基于电荷的存储器技术而言,新型存储器技术基于存储元件的其他物理属性。举例来说,磁阻 RAM (MRAM) 的存储器元件由两个铁磁板组成,这两个铁磁板由一层薄薄的绝缘层隔离。每片铁磁板都能保有磁化属性,一个是永久性的,另一个可有外部场改变,从而存储数据。通过测量元件电阻即能读取存储的数据。MRAM 存取速度类似于 SRAM,密度类似于 DRAM。相比于闪存存储器,MRAM 运行速度更快,而且不会因编程而被磨损。

软件运行在 Zynq SoC 的 ARM A9 处理器上,而存储器控制器内核则用可编程逻辑创建。

要求分析

在设计 MRAM 测试芯片评估方案时,我们决定采用 Zynq SoC 方法,这主要出于以下考虑:

• ZC706 开发板的 FPGA 夹层卡 (FMC) 接口通过 FMC 子卡提供进出存储器测试芯片的高速信号发送功能。

• Zynq SoC 的可编程逻辑 (PL) 部分能构建参数化存储器控制器内核。这对满足测试芯片差异化存取速度的要求很重要。

• Zynq SoC 的处理系统 (PS) 包括两个 ARM® A9 内核,能通过软件修改测试芯片存取速度。

• PS 也能构建完整的计算系统,这对满足测试系统在全面计算环境下测量芯片存取速度的影响的要求很重要。

硬件和系统架构

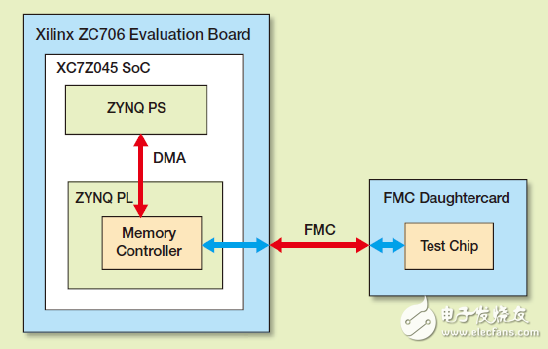

芯片测试环境的硬件架构如图 1 所示。软件运行在 Zynq SoC 的 ARM A9 处理器上,而存储器控制器内核用可编程逻辑创建。我们在 PS 和控制器内核之间建立 DMA 通道,以便在彼此之间能方便地移动大数据块。存储器测试芯片位于 FMC 子卡上,其通过 FMC 接口与存储器控制器内核通信。

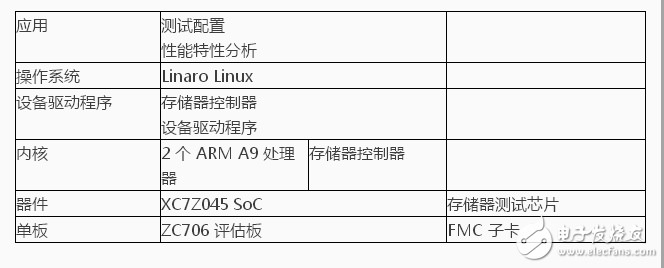

系统架构如图 2 所示。底部三层为硬件层,顶部三层为软件层。我们选择 Linux 为 *** 作系统,因为这是一种开源系统,源代码能根据需要修改。虽然目前开发阶段没有进行修改,但今后这种新型存储器芯片发挥独特属性优势时或许能用得上。

图 1 – 测试环境的硬件架构

图中文字如下:

赛灵思 ZC706 评估板

XC7Z045 SoC

ZYNQ PS

DMA

ZYNQ PL

存储器控制器

FMC

FMC 子卡

测试芯片

图 2 – 测试环境的系统架构

我们在应用层编写的软件分为两类。一类用于配置存储器控制器内核;另一类涉及存储器芯片和整体系统性能的特性分析。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)