ZYNQ 7系列所有可编程器件均可以在安全模式下通过静态存储器配置或者在非安全模式下通过JTAG或者静态存储器配置。

(1)JTAG模式主要用于开发和调试

(2)NAND、并行NOR、串行NOR、SD卡闪存均可以用作器件的启动

处理器系统启动主要包括两个阶段:

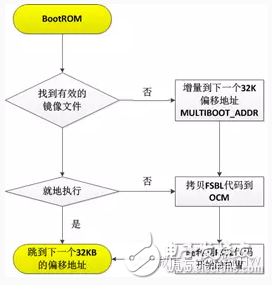

(1) Stage-0的启动代码存储在内部的BOOTROM,这部分启动代码用于ARM处理器和必 要的外设的配置以便可以开始从启动器件中取出第一阶段引导加载程序的启动代码。可编程逻辑部分不能被BootROM配置.BootROM是不可写的

(2)第一阶段引导加载程序的启动代码通常被存储在一个flash存储器中,或者可以通过JTAG下载。BootROM代码将FSBL的启动代码从选定的flash存储器中拷贝到片上存储器中。拷贝到OCM(片上存储器)中的FSBL的代码的大小被限制在192kb。FSBL开始执行的时候,OCM的全部256kb的空间全部可以使用,剩余的64kb的存储空间也不再被保留。

FSBL的启动代码是受完全使用者控制的,通常被称作用户启动代码。这提供给使用者足够的灵活性以实现其系统所需的任何的启动代码。

XILINX提供一个参考的FSBL的启动代码帮助使用者实现自己的需求。这部分启动代码包括PS部分外设的初始化代码,FSBL详细的初始化时序请参阅SDK提供的FSBL代码。FSBL的启动镜像可以包括一个用于初始化PL部分的比特流。

PL并没有要求必须在这一阶段进行配置,因为在PL没有配置的时候,PS是完全可 *** 作的。我们可以自定义FSBL的启动代码,从而使用其他的PS外设,例如以太网、USB、或者标准输入和输出IO口对PL进行配置。

存在以下几种可能的启动模式:

(1)PS作为主机的非安全模式

(2)PS作为主机的安全模式

(3)通过JTAG/PJTAG启动

ZYNQ 7系列所有可编程器件均支持安全模式和非安全模式两种启动流程,如下:

(1)Stage-0启动(BOOTROM)

(2)第一阶段引导加载程序

(3)可选择阶段

Stage-0启动的流程图如下:

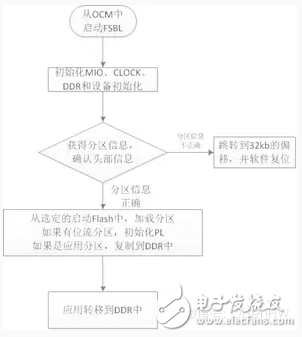

第一阶段引导加载程序(FSBL)开始于boot之后。启动代码被BOOTROM拷贝到片上存储器中,FSBL的主要任务:

(1)使用XPS提供的PS的配置数据进行系统的初始化

(2)使用比特流文件进行PL的配置

(3)向DDR存储器中加载第二阶段引导加载程序或bare-metal引用代码

(4)执行第二阶段引导加载程序或者bare-metal应用

FSBL的大致流程如下

FSBL的特性

(1)FSBL Fallback

为了从error中恢复,FSBL会进行一次fallback,并加载另一个存储在flash存储器中可启动的镜像文件。FSBL更新mulTIboot寄存器,并产生一个软件复位,以便bootrom执行并加载一个可执行的现存的镜像文件。

(2)FSBL MulTIboot

FSBL存在一种机制:提供一个可以mulTIboot的寄存器,寄存器中列出了flash中多个可以启动的镜像文件,并且可以更新mulTIboot的地址以指向boot的镜像文件,从而可以保证bootrom可以从flash存储器中加载所需的镜像文件。

(3)FSBL Hooks

FSBL的hooks提供了一个插入曾经使用过的函数的简单的方法。FSBL的hook函数存在于fsbl_hook.c文件中。

fsbl_hook.c文件中主要包括以下的函数:

FsblHookBeforeBitstreamDload:该函数用于在比特流文件被下载之前。可以在比特流文件被下载之前向程序中加载定制的代码。

FsblHookAfterBitstreamDload: 该函数用于比特流文件被下载之后。可以在比特流文件被下载之后向程序中加载定制的代码。

FsblHookBeforeHandoff: 该函数用于FSBL转向应用之前。可以在FSBL转向应用之前向程序中加载定制的代码。

通过使用这些函数,用户可以在FSBL的流程时序中加载任意的初始化代码。

(4)DDR 错误检查与纠正

可以通过XPS ZYNQ tab使能DDR的错误检查与纠正:FSBL负责DDR的初始化。

因为FSBL并不对DDR进行重新构图,所以DDR从大于1MB的位置启动。应用必须从1MB的位置开始使用DDR,如果需要重新构图的话,就初始化小于1MB的存储器用来进行错误检查与纠正。

ZYNQ的PS的配置

使用Zynq的配置用户界面,XPS生成用于初始化MIO和SLCR(系统级的控制寄存器)寄存器。在XPS的工程目录下,需要特别关注的文件有:ps7_init.c和ps7_init.h,这两个文件可以用来初始化CLK,DDR和MIO。ps7_init.tcl执行的初始化和ps7_init.c一样。ps7_init.tcl文件,这个文件可以用来初始化CLK、DDR和MIO。ps7_init.tcl执行的初始化和ps7_init.c一样。

注意:Tcl文件在使用XMD调试程序的时候比较有帮助。例如,你可以运行ps7_init.tcl文件,之后加载应用程序后加载应用程序到DDR中,然后进行调试。这种情况下,完全没到DDR中,然后进行调试。这种情况下,完全没有必要进行FSBL。

ps7_init.html,该文件描述了初始化的数据。

镜像文件的格式主要包括启动镜像文件的格式和分区头表文件格式两个方面。

启动镜像文件格式包含:

(1)BootROM的头

(2)FSBL的镜像

(3)一个或者多个分区镜像

(4)未使用的空间(如果有)

下图展示了启动镜像格式的布局

分区头表:

分区头表是一个结构体数组包含如下表所示的数据。对于每一个分区存在一个结构体,包括FSBL分区,表中的最后一个结构体被所有NULL值的标记。

偏移量 名称 描述

0x00 分区数据大小 分区数据长度(字长表示)

0x04 写数据长度 解密的分区中的数据长度(字长表示),这个值和未解密的分区的数据长度一致

0x08 分区总大小 对应于这个分区头表的启动镜像分区的大小,可能包含一些未使用的留作扩展的空间

0x0c 引导地址 向存储中引导镜像的地址,这个地址就是PS数据写入的地方,这部分对PL的比特流分区不适用

0x10 执行地址 可执行文件启动的位置,这部分对PL的比特流分区不适用

0x14 分区偏移量 从分区数据所对应的引导映像的开始到此分区头表起始的字节数

0x18 属性 第5位被设置为比特流分区,第4位被设置为PS分区,其余保留

0x1c 分区数据段数 分区数据中独立加载的数据段数目,此分区只适用于内存加载分区数据

0x20到0x3b 保留 保留

0x3c 校验 用于第一段启动加载程序检查头部的有效性,校验是对此结构中的所有以前值的和按位非

启动镜像的产生

Bootgen是一个为Zynq的配置组织启动镜像的工具。Bootgen依据启动镜像格式文件中定义的格式将一个bit文件和ELF文件合并成为一个单独的启动镜像文件,从而完成ZYNQ flash设备的烧写。

Bootgen自动的将数据结合到启动镜像中,将启动镜像下载到flash存储器中之后,Zynq的BootROM和FSBL使用这个镜像,并自动地从中提取出烧写的数据镜像,并对ZYNQ的设备进行配置。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)