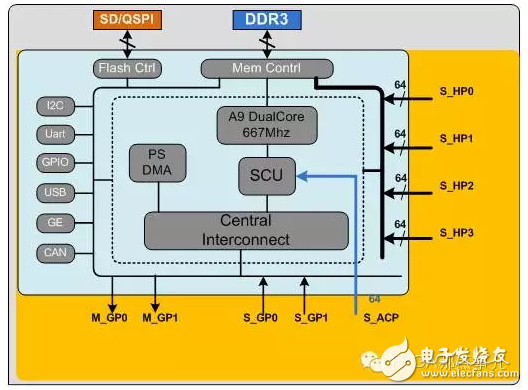

Zynq芯片中,PS(ProcessorSystem)和PL(Programmable Logic)之间提供了一共9个双向读写的通信端口,他们分别是:

M_GP0 &M_GP1

S_GP0 &S_GP1

S_AXI_HP0-3

S_AXI_ACP

这些端口的特性和适合的使用场景都不太一样,其中M_GP适合CPU和FPGA之间少量的数据通信,S_HP用来进行大批量的数据交互,S_GP很少用到,S_ACP同S_HP类似,但是它可以保证CPU和DDR3之间的Cache一致性。

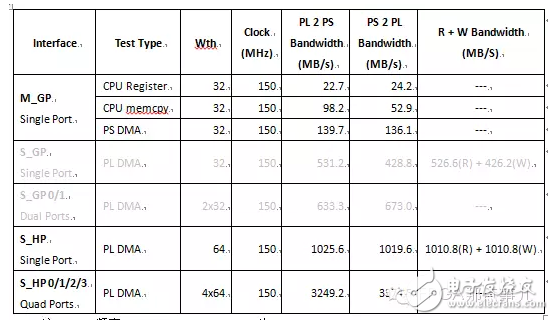

那么这些接口实际使用时,它们能提供的最大吞吐量如何呢,下标给出了一个实测的数据:

注: CPU频率667Mhz,CPU ClockRaTIo为6:2:1,DDR Date Rate1066Mhz,PL-PS AXI Clock 150Mhz

S_ACP和S_HP的数据比较接近

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)