赛灵思 Zynq®-7000 All Programmable SoC 系列代表了嵌入式设计的新局面,为嵌入式系统工程设计群体带来前所未有的高性能和灵活性。这些产品在单个器件上集成了特性丰富的双核 ARM® Cortex-A9 MPCore处理系统和赛灵思可编程逻辑。3,000 多个互联点将片上处理系统 (PS) 与片上可编程逻辑 (PL) 相连,使两个片上系统之间的性能达到了任何双芯片处理器 FPGA 都无法匹敌的高度。赛灵思在 2011 年发布这款 Zynq SoC 器件时,便立即得到了很多精通硬件设计语言和方法以及嵌入式软件开发的嵌入式系统工程师和架构师的追捧。如今,首款 Zynq SoC 已被用于无线基础设施、智能工厂和智能视频/视觉等多种嵌入式应用领域,并且快速成为高级驾驶员辅助系统约定俗成的标准平台。

为了让这款性能卓越的器件能够被具有很强软件背景但没有 HDL 经验的嵌入式工程师所用,赛灵思在今年年初推出了基于 Eclipse 的 SDSoC集成开发环境,使软件工程师能够对 Zynq SoC 中的可编程逻辑和 ARM 处理系统进行编程。

我们仔细了解一下 Zynq SoC [1] 的特性以及软件工程师如何利用 SDSoC 环境来创建用任何其他“处理器+FPGA”系统均无法实现的系统设计。为进行研究,我们将使用包含一个 Zynq Z-7020-1 器件的赛灵思 ZC702 评估板 [2] 作为硬件平台。

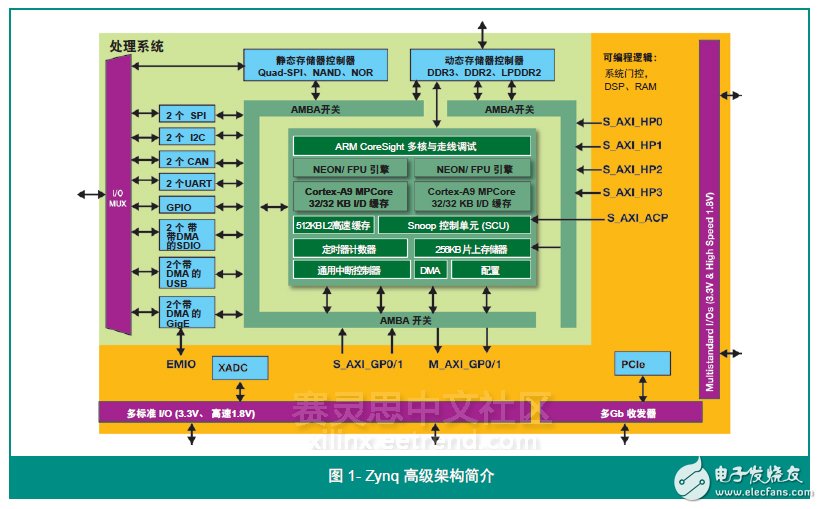

如图 1 所示,Zynq SoC 包含两大功能模块:PS(包含应用处理器单元、存储器接口、外设和互联)和 PL(传统的 FPGA 架构)。

PS 和 PL 通过与 ARM® AMBA® AXI4 接口兼容的互联链路紧密耦合在一起。四个高性能 (HP) AXI4 接口端口将 PL 连接到 PS 中的异步 FIFO 接口 (AFI) 模块,从而在 PL和 PS 存储器系统(DDR 和片上存储器)之间提供一条高吞吐量的数据路径。AXI4 加速一致性端口 (ACP) 允许直接从 PL 主设备对 L1 和 L2 高速缓存进行低时延的一致性访问。通用 (GP) 端口包含可从 PS 和 PL 访问的低性能通用端口。

在传统的以硬件设计为核心的流程中,通过使用赛灵思的 Vivado® Design Suite 在 Zynq SoC 上设计嵌入式系统大致需要四个步骤:

1. 系统架构师确定硬件-软件分区方案。计算密集型算法最适合硬件。特性分析结果是鉴别性能瓶颈以及在数据移动成本与加速优势之间进行权衡研究的基础。

2. 硬件工程师处理被分到硬件中的功能,并将它们转换或设计成 IP 核,例如,用 Vivado 取代VHDL 或 Verilog ;用 Vivado 高层次综合 (HLS) 实现 C++/C++ 高层次综合[3],或者用 Vivado System Generator for DSP 实现模型化设计 [4]。

3. 然后,工程师使用 Vivado IP Integrator [5]创建整个嵌入式系统的模块化设计。整个系统的开发需要用到不同的数据移动工具(AXI-DMA、AXI Memory Master、AXI-FIFO 等),以及连接 PL IP 与 PS 的AXI 接口(GP、HP 和 ACP)。一旦 IP Integrator 中所有设计规则检查都通过,就可将项目导出至赛灵思软件开发套件 (SDK) [6]。

4. 软件工程师使用赛灵思 SDK 开发针对 PS 中 ARM处理器的驱动程序和应用。

最近几年,赛灵思对 Vivado Design Suite 的简便易用性实现了显著提高,该套件能够让工程师缩短 IP 开发时间以及 IP 模块连接步骤(上述步骤 2 以及步骤 3 的部分内容)。就 IP 开发而言,采用这些最新设计技术(例如在 Vivado HLS 工具中实现 C/C++高层次综合;用 Vivado System Generator for DSP 实现模型化设计)可以显著缩短开发和验证时间,同时让设计团队能够使用高层次抽象探索更大的架构范围。对于使用 VHDL 或 Verilog 需要数周才能完成的设计,利用新型工具只需数天就能完成。

SDSoC 环境会自动安排所有必要的赛灵思工具,以生成针对 Zynq SoC 的完整软硬件系统,而且所需的用户介入程度很小。

赛灵思通过 Vivado IP Integrator 可进一步强化流程。Vivado Design Suite 的这个功能使设计人员只需要在图形用户界面 (GUI) 中连接 IP 模块,就可以设计复杂的硬件系统(嵌入式或非嵌入式),从而实现快速的硬件系统集成。

新的 Vivado Design Suite 功能可帮助设计与开发团队简化 Zynq SoC 的使用。但对于以硬件为中心的优化流程而言,要缩短探索不同数据移动工具和 PS-PL接口(步骤 3 的一部分)以及写入和调试驱动程序与应用(步骤 4)所需的开发时间,办法并不多。如果整个系统不能满足吞吐量、时延或占位面积等方面的设计要求,那么设计团队不得不修改步骤 3 中的系统连接,以重构硬件架构。这些修改会不可避免地导致步骤 4 中的软件应用发生变化。有些情况下,加速不足或者硬件利用率过高会迫使开发团队重新考虑最初的软硬件分区。多个硬件和软件团队将不得不再次反复设计系统,以探索可能满足最终要求的其他架构。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)