摘 要: 设计了一种针对具有大数据量特点图像数据采集、存储及长线回读的测控系统。在控制信号的作用下,此测控系统将CMOS传感器采集的大容量数据存储到Flash芯片中。存储完成后,通过LVDS总线,将Flash芯片中存储的数据回传到上位机进行存盘并显示。实验证明,此系统稳定性高,在工业控制领域具有借鉴意义。

0 引言

随着科学技术的发展,视觉技术被广泛应用于军事、工业以及测控领域。视觉是人们主要的信息源,通过图像采集系统对周围环境图像数据进行采集,这样机器能够替代人类获得环境信息,此种系统被广泛应用于测控系统,以获得飞行器的环境参数。利用高性能的FPGA控制图像数据的采集与图像数据处理,通过交错双平面技术对处理后的图像数据进行存储,通过USB总线,将处理后的数据传输给上位机进行解包并显示。

1 系统的总体设计

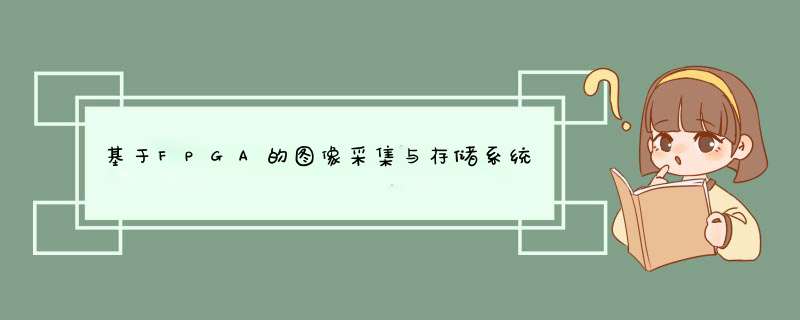

系统工作过程:采集存储模块的FPGA通过模拟IIC时序,对CMOS模拟传感器进行初始化与配置,并采集图像数据,通过信号调理电路将采集的模拟信号进行滤波放大,并将调理放大的信号进行A/D转换后输出给FPGA,FPGA将接收的数据通过内部FIFO缓存后传输给Flash芯片进行存储。FPGA回读Flash芯片内的数据,通过LVDS总线(型号DS92LV1023)发送给监控读数模块,通过USB接口(型号CY7C68013)传输给上位机,由上位机对图像进行解码显示。系统的原理框图如图1所示。

FPGA采用XILINX公司的XC3S1400AN,内部包含有丰富的RAM资源,便于数据采集[1-3]。

2 CMOS图像数据采集模块

通过FPGA对CMOS图像采集模块进行逻辑控制。其中采集模块主要完成对视频图像的采集,对采集到的信号进行模数转换,并对此信号进行低通滤波及放大后[4-7]传输给图像数据存储模块进行存储。

在本文的系统设计中,对图像数据的采集是核心模块。视频前端应用CMOS图像传感器(型号OV7670),输出的图像数据最高为30帧/s,30万像素,芯片内部的寄存器达201个,通过FPGA控制单片机对传感器寄存器进行配置。单片机采用IIC总线为传感器寄存器串行传输数据,在对IIC总线时序控制中,利用54个SDA时钟传输32 bit的配置数据,其中前两个时钟周期完成时序模块的初始化,延时4个周期后,启动串行数据的传输,传送完一个字节数据后等待从接收器(CMOS图像传感器)的应答信号,当单片机确定从接收器正确接收后,启动发送下一个字节的配置数据,直到发送完4个字节的配置数据后,发送终止信号,结束IIC总线的传输,完成传感器的初始化,从而控制图像数据的质量、图像数据的制式以及数据的传输方式。其中IIC总线传输模块的时钟为30 kHz。

CMOS图像传感器将采集到的光信号转换为模拟信号,被转换的模拟信号很微弱,为达到A/D转换芯片对处理信号电平的要求,需要对传感器输出的模拟信号进行放大处理,经A/D转换芯片将模拟信号转换成数字信号输出。FPGA的解码部分通过控制3种同步信号(像素时钟同步信号、行同步信号和场同步信号),进而得到8 bit的RGB制式的图像数据信号。图像传感器的分辨率为640×480,行同步信号为“1”时有效,每行显示的有效数据是640 bit;每列显示的有效数据是480 bit,场同步信号为“0”时输出转化后的有效数据,当其变为“1”时,表明一帧图像数据传输完成。采集到的数据通过FPGA芯片的内部FIFO缓存。

3 图像数据存储模块

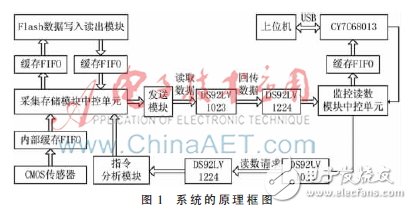

本文采用的FPGA片内存储器有限,考虑到大数据量的图像数据,需要外部扩展存储器,选用K9WBG08U1M型号的Flash,此Flash最大存储4 GB图像数据,以页为单位对数据进行读写,以块为单位对数据进行擦除,包含3种地址控制信号(列地址、行地址和块地址)。图像存储模块在上电初始化后,FPGA控制时序擦除Flash内存,并等待存储视频前端采集到的图像数据。采用交错双平面式对接收到的图像数据进行存储,将1片4 GB的Flash分成2片2 GB的Flash,对其中一片Flash进行写 *** 作的同时对另一片Flash进行读 *** 作,此种交错方式使输入输出不间断,实现图像数据的无缝处理,提高数据传输与处理的效率。

4 监控读数模块

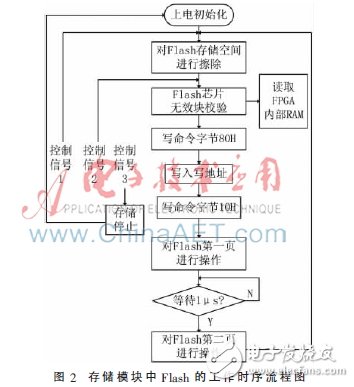

通过综合考虑,图像数据存储模块与监控读数模块通过低压差分传输方式(LVDS)进行数据的传输,此种传输方式适用于高速短距离传输,但是,在利用普通双绞线进行数据的传输时,信号的传输损耗随着信号频率的增加而增加。基于此种限制,在图像数据的发送端加入驱动以增强信号,在图像数据的接收端采用均衡补偿法补偿信号在传输过程中的损耗。

此监控读数模块采用LVDS接口和422接口与图像数据存储模块进行通信。LVDS接口主要负责存储命令的下发和回读存储模块的图像数据,422接口主要负责对存储模块状态的监控,通过回读存储模块的状态信息以确定存储模块是否正常工作。图3所示为监控读数模块与数据存储模块的LVDS接口示意图。存储模块接收到读数命令,通过LVDS接口,将数据传输给监控读数模块,监控读数模块通过检测数据的高两位判断是否为有效数据。若为有效数据,将此数据存储到外部的FIFO中,若为无效数据,则丢弃。监控读数模块向存储模块发送启动存数数据命令后,数据存储模块通过422接口将本身的状态信息发送给数据监控模块,通过这些状态信息能够判断存储模块是否正常工作。

5 系统测试结果

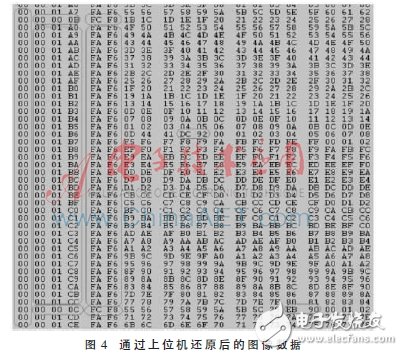

在对本系统的硬件和软件模块调试成功后,对系统的总体功能进行测试。CMOS模拟传感器对图像数据进行采集后,通过数据存储模块对采集到的数据进行存储,由监控读数模块通过LVDS接口回读图像数据,并将此数据通过USB接口上传给上位机,上位机对此数据进行解码并显示,图4所示为还原后的图像数据。其中FAF6为帧开始标志,帧标志前面的3个字节是帧计数。

6 结论

本文利用CMOS传感器实现了对图像数据实时采集的要求。应用K9WBG08U1M型号的Flash芯片通过交叉双平面技术对此图像数据进行存储,实现了数据的无缝传输,以流水线的数据传输方式提高了本系统的传输效率。监控读数模块通过LVDS接口和422接口对存储模块的数据进行回读并在上位机上显示。系统充分利用了具有高性能的XC3S1400AN(所用FPGA型号)芯片,提高了系统的运行速度,具有很高的参考价值。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)