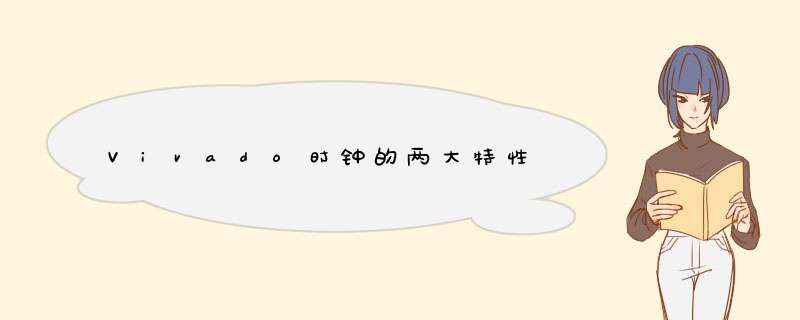

FPGA内部时钟通常由外部时钟源提供,经过PLL/MMCM生成内部所用时钟。从时钟源比如晶振或者上游芯片经过板级走线到FPGA的专用时钟管脚,这个过程必然有板级走线延迟;由create_clock定义的时钟端口到同步原件的时钟端口也必然有延迟。这两类延迟共同构成了时钟延迟,前者为时钟源延迟(Source Latency),后者为时钟网络延迟(Network Latency)。两者的关系如下图所示。

对于时钟网络延迟,Vivado为自行分析计算。对于时钟源延迟,可通过set_clock_latency来定义。如下Tcl脚本所示。

# Minimum source latencyvalue for clock sysClk (for both Slow and Fast corners)

set_clock_latency -source-early 0.2 [get_clocks sysClk]

# Maximum source latencyvalue for clock sysClk (for both Slow and Fast corners)

set_clock_latency -source -late 0.5 [get_clocks sysClk]

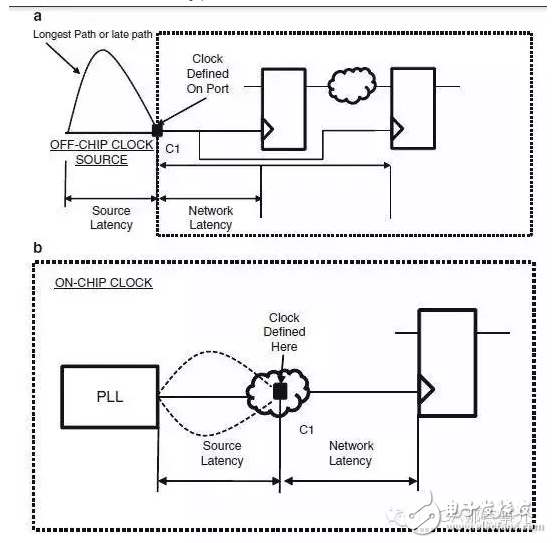

我们先看一下时钟不确定性的计算公式,如下图红色方框所示,在Vivado中打开时序路径,选中其中的Clock Uncertainty后面的数据,点击即可出现明确的计算公式。

这个公式表明,时钟的不确定性主要的构成因素为时钟抖动,包括输入抖动(Input Jitter)和系统抖动(System Jitter)。时钟抖动的具体概念可形象地用如下图表示,时钟周期为10ns的理想的时钟上升沿应该在0ns,紧邻之的下降沿应该在5ns,但因为抖动,上升沿可能会出现在0.1ns,下降沿出现在5.1ns。

在Vivado中可通过set_clock_uncertainty来设定时钟的不确定性。如下Tcl脚本所示。

set_clock_uncertainty-setup 0.213 [get_clocks wbClk]

set_clock_uncertainty-hold 0.167 [get_clocks wbClk]

设定时钟的不确定性的一个好处是可以在时序分析时时序过约束,而避免直接修改时钟周期。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)